# SM3110 Technical Reference

Preliminary

## **Copyright Notice**

Copyright 1999 by Silicon Magic Corporation. All rights reserved.

This technical reference manual is the intellectual property of Silicon Magic Corporation. You may not reproduce, transmit, transcribe, store in a retrieval system or translate into any language or any computer language in any form or by any means - electronic, mechanical, magnetic, optical, chemical, manual or otherwise - any part of this publication without the express prior written permission of Silicon Magic Corporation.

| Revision Number | Contents      | Contributer / Writer | Date      |

|-----------------|---------------|----------------------|-----------|

| 1.0.0.0         | First Release | Staff / Inc          | 8/12/1999 |

# **Table of Contents**

| 1     | SM3110 Features Overview              |

|-------|---------------------------------------|

| 1.1   | Features Overview 1-2                 |

| 2     | Architecture Overview                 |

| 2.1   | System Configuration 2-2              |

| 2.2   | Internal Configuration 2-3            |

| 2.2.1 | Host Interface 2-4                    |

| 2.2.2 | Embedded Memory 2-5                   |

| 2.2.3 | VGA Module 2-8                        |

| 2.2.4 | 2D Rendering Engine 2-9               |

| 2.2.5 | 3D Rendering Engine 2-10              |

| 2.2.6 | Display Pipeline                      |

| 2.2.7 | Video Input 2-13                      |

| 2.2.8 | Motion Compensation 2-14              |

| 2.2.9 | ROM Port                              |

| 2.3   | Additional Features 2-16              |

| 2.3.1 | Power Management 2-16                 |

| 2.3.2 | Board-level Test Functions            |

| 2.3.3 | Clocks                                |

| 2.3.4 | Inter-IC (I <sup>2</sup> C) Interface |

|       |                                       |

| 3       | Data Sheet                         |

|---------|------------------------------------|

| 3.1     | Pin Descriptions                   |

| 3.1.1   | AGP/PCI Interface                  |

| 3.1.2   | Panel Interface                    |

| 3.1.3   | ROM Interface                      |

| 3.1.4   | ZV Port                            |

| 3.1.5   | CRT Interface 3-5                  |

| 3.1.6   | Reference Clock Input 3-5          |

| 3.1.7   | Programmable I/O Pins              |

| 3.1.8   | Testing Pins 3-6                   |

| 3.1.9   | Reserved Pins                      |

| 3.1.10  | Digital Power and Ground Pins      |

| 3.1.11  | Analog Power and Ground Pins       |

| 3.1.12  | Pad Descriptions                   |

| 3.1.13  | Alternate Pad Function 3-9         |

| 3.1.14  | Pin Assignment (by pin number)     |

| 3.1.15  | Pin Assignment (by signal name)    |

| 3.2     | Electrical Specifications 3-18     |

| 3.2.1   | Maximum DC Specifications          |

| 3.2.2   | Normal Operating DC Specifications |

| 3.2.3   | DC Characteristics 3-19            |

| 3.2.4   | AC Timing 3-21                     |

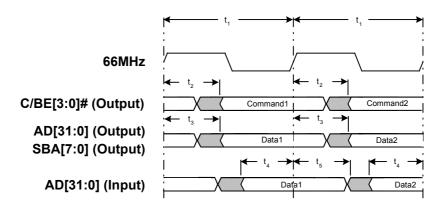

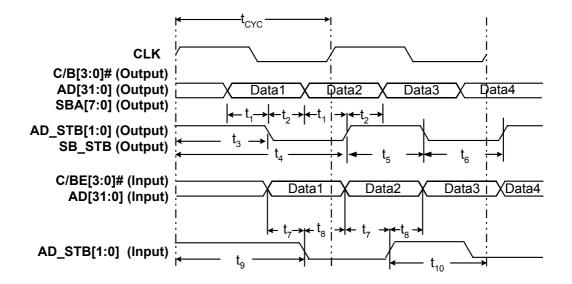

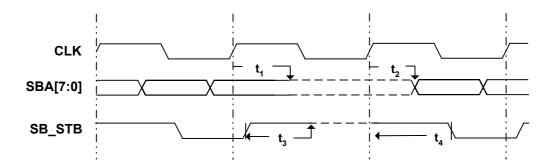

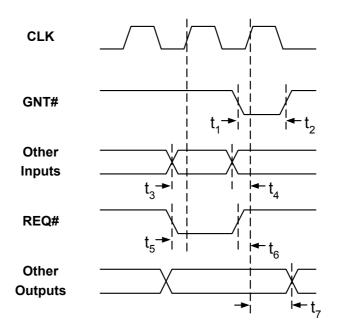

| 3.2.4.1 | AGP Timing 3-21                    |

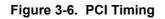

| 3.2.4.2 | PCI Timing 3-24                    |

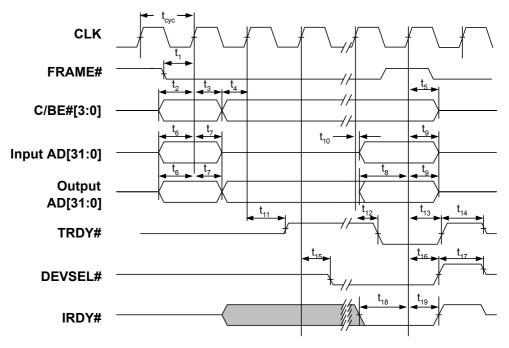

| 3.2.4.3 | PCI Clock Timing 3-26              |

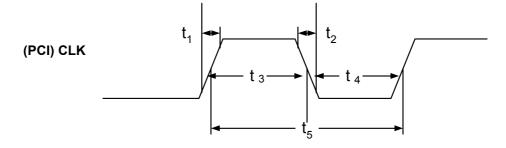

| 3.2.4.4 | Panel Interface                    |

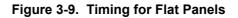

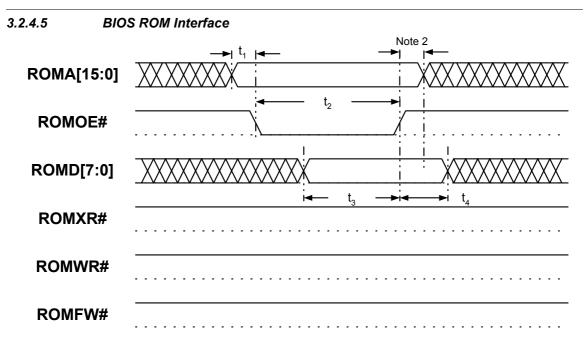

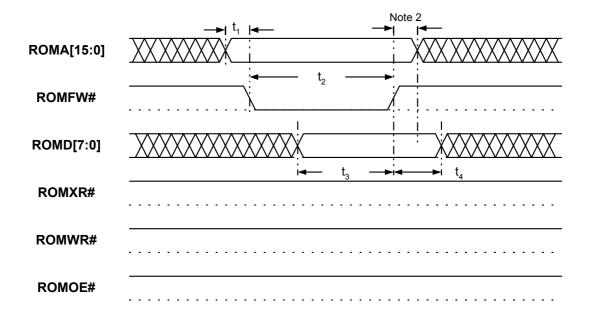

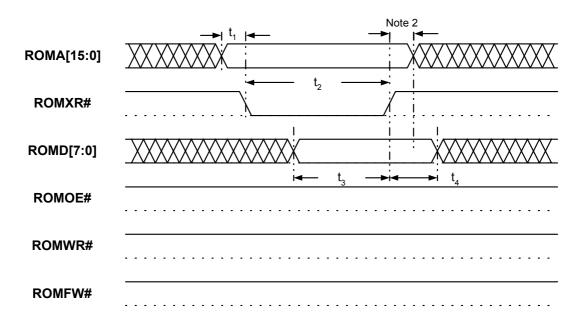

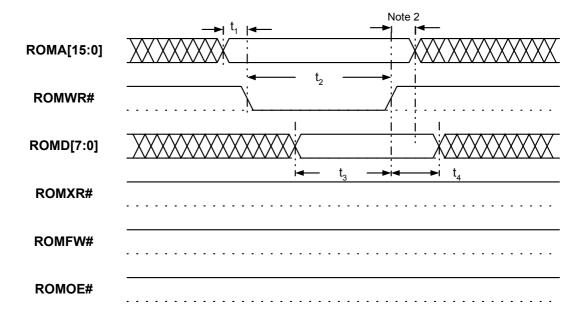

| 3.2.4.5 | BIOS ROM Interface 3-28            |

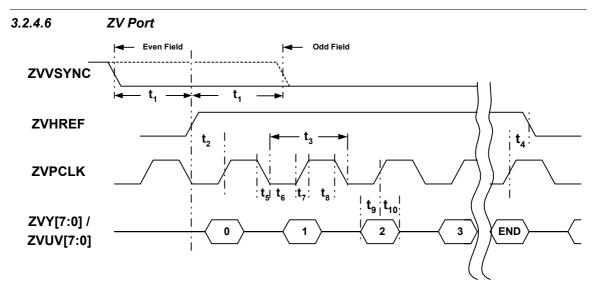

| 3.2.4.6 | ZV Port                            |

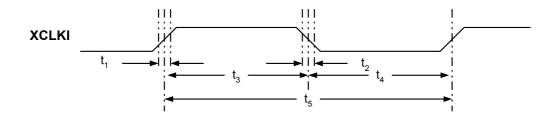

| 3.2.4.7 | Reference Clock 3-33               |

| 3.2.4.8 | Reset                              |

| 3.3     | Mechanical Specifications 3-35     |

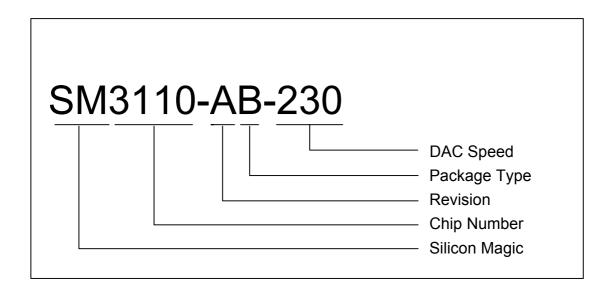

| 3.4     | Ordering Information               |

| 4        | Register Summary                                  |         |

|----------|---------------------------------------------------|---------|

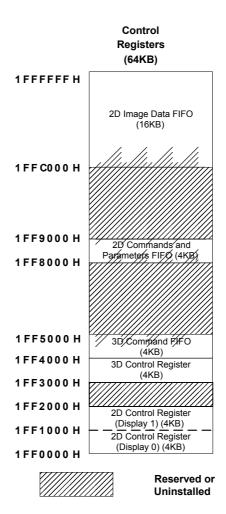

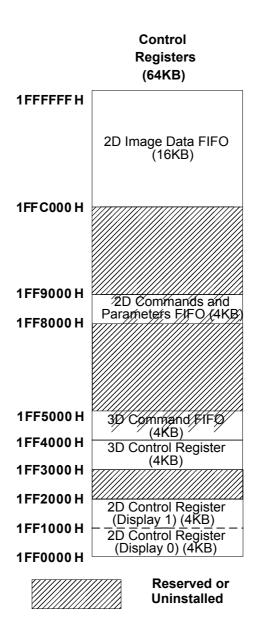

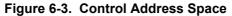

| 4.1      | Control Address Space Overview                    |         |

| 4.2      | Register Listing for Control Address Space        | 4-4     |

| 4.2.1    | 2D Control (Display 0, Display 1) (1FF0000H)      | 4-5     |

| 4.2.1.1  | Status/Control (+000H)                            | 4-6     |

| 4.2.1.2  | Reserved (+100H)                                  |         |

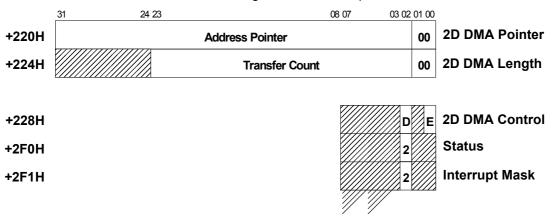

| 4.2.1.3  | Host Bus Master (+200H)                           | 4-14    |

| 4.2.1.4  | VGA Registers (+300H)                             |         |

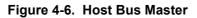

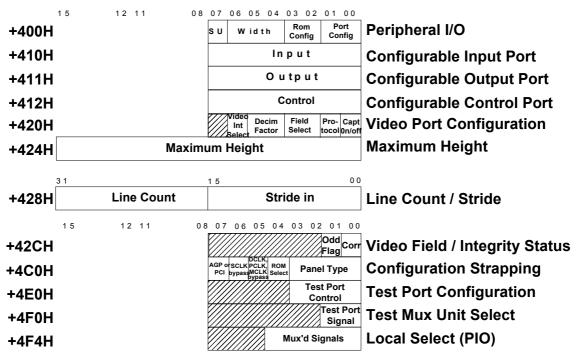

| 4.2.1.5  | Peripheral Ports (+400H)                          |         |

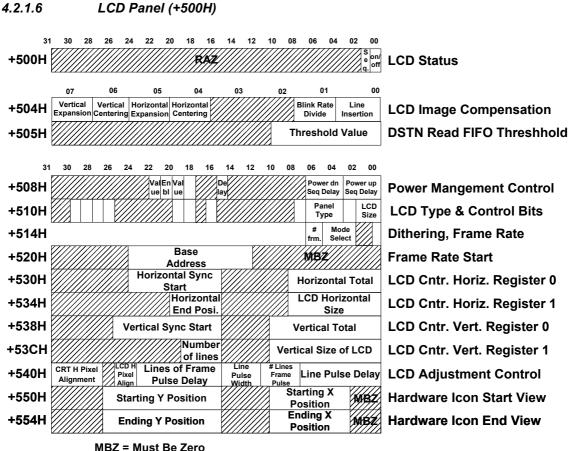

| 4.2.1.6  | LCD Panel (+500H)                                 |         |

| 4.2.1.7  | Reserved (+600H)                                  |         |

| 4.2.1.8  | Reserved (+700H)                                  |         |

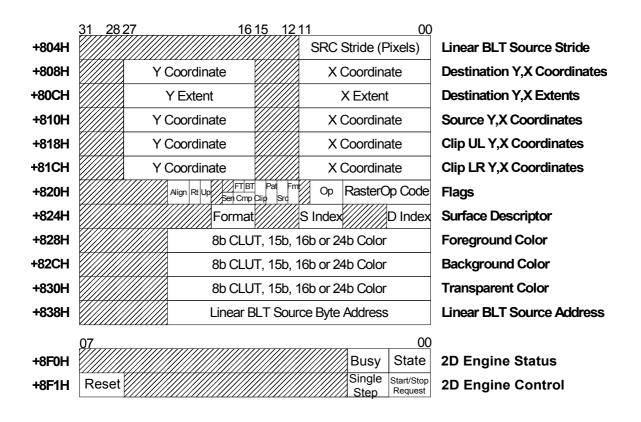

| 4.2.1.9  | 2D Rendering Engine (+800H)                       | 4-31    |

| 4.2.1.10 | Memory Controller (+900H)                         |         |

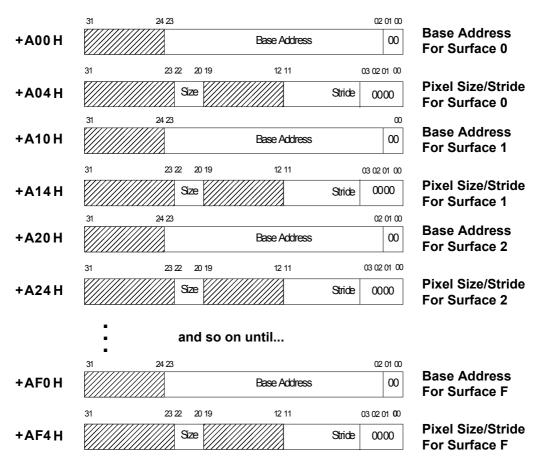

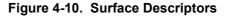

| 4.2.1.11 | Surface Descriptors (+A00H)                       | 4-43    |

| 4.2.1.12 | Channel Descriptors (+B00H)                       |         |

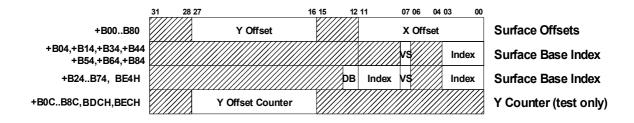

| 4.2.1.13 | Buffer Descriptors (+C00H)                        | 4-48    |

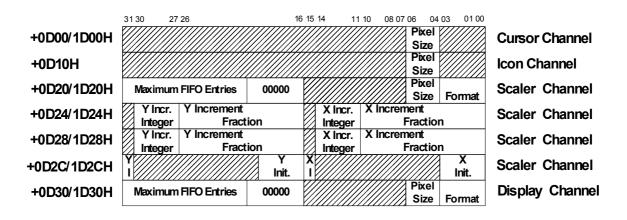

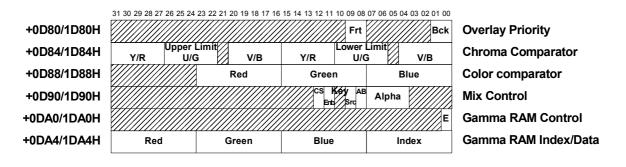

| 4.2.1.14 | Display Control (+D00H)                           |         |

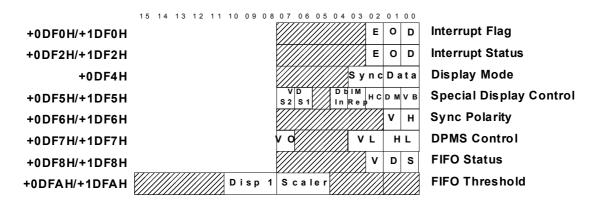

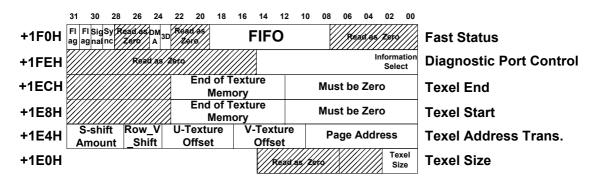

| 4.2.1.15 | Display Viewports and Timing (+E00H)              | 4-68    |

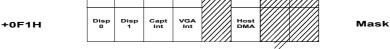

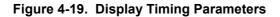

| 4.2.1.16 | PCI/AGP Configuration Registers (+F00H)           | 4-76    |

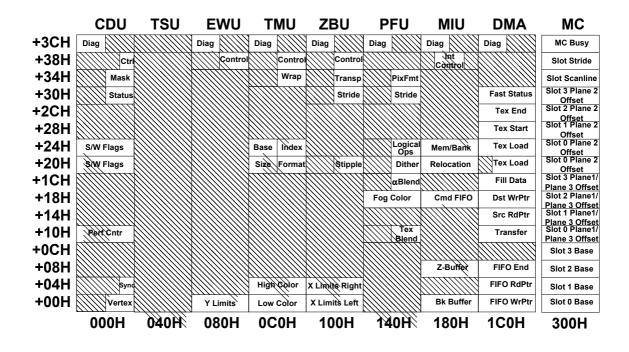

| 4.2.2    | 3D Control (1FF3000H)                             | 4-84    |

| 4.2.2.1  | Command Decode Unit (+000H)                       |         |

| 4.2.2.2  | Triangle Setup Unit (+040H)                       | 4-91    |

| 4.2.2.3  | Edge-Walking Unit (+080H)                         |         |

| 4.2.2.4  | Texture Mapping Unit (+0C0H)                      |         |

| 4.2.2.5  | Z Buffer Unit (+100H)                             | 4-96    |

| 4.2.2.6  | Per Fragment Unit (+140H)                         |         |

| 4.2.2.7  | Memory Interface Unit (+180H)                     | . 4-104 |

| 4.2.2.8  | DMA (+1C0H)                                       |         |

| 4.2.2.9  | Motion Compensation (+300H)                       |         |

| 4.2.2.10 | Stipple Mask Array (+400H)                        |         |

| 4.2.2.11 | Texture Map LOD Table Array (+580H)               |         |

| 4.2.2.12 | Temporary Array for Triangle Setup Unit (+5C0H) . |         |

| 4.2.3    | 3D Command/Parameter FIFO (1FF4000H)              |         |

| 4.2.4    | 2D Command/Parameter FIFO (1FF8000H)              |         |

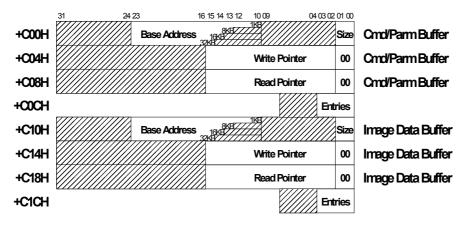

| 4.2.5    | 2D Image Data FIFO (1FFC000H)                     | . 4-117 |

| 4.3     | Standard VGA Registers          | 4-118 |

|---------|---------------------------------|-------|

| 4.3.1   | Register Locations              | 4-118 |

| 4.3.2   | General Registers               | 4-120 |

| 4.3.3   | CRT Controller (CRTC)           | 4-122 |

| 4.3.3.1 | VGA CRTC Resolution Limitations | 4-122 |

| 4.3.3.2 | CRTC Index/Data Registers       | 4-123 |

| 4.3.4   | Sequencer                       | 4-128 |

| 4.3.5   | Graphics Controller             | 4-131 |

| 4.3.6   | Attribute Controller            | 4-137 |

| 4.3.7   | Enhanced VGA Registers          | 4-140 |

| 4.3.7.1 | Enhanced Register Access Enable | 4-140 |

| 4.3.7.2 | Enhanced Control Access         | 4-141 |

| 4.3.7.3 | Bank Offset                     | 4-142 |

| 4.3.7.4 | User-Defined Scratch Registers  | 4-143 |

| 4.3.7.5 | CRTC Test                       | 4-143 |

|         |                                 |       |

| 5        | BIOS Specifications                                  |       |

|----------|------------------------------------------------------|-------|

| 5.1      | Overview                                             | . 5-2 |

| 5.1.1    | SM3110 Specific Extended BIOS Functions              | . 5-5 |

| 5.1.2    | Standard VGA BIOS Functions                          | . 5-6 |

| 5.1.3    | VESA BIOS Extended Functions                         | . 5-8 |

| 5.1.4    | SCRATCHPAD Register Usage                            | . 5-9 |

| 5.2      | VGA BIOS Functions                                   | 5-12  |

| 5.2.1    | SM3110 Extended BIOS Functions (5Fh)                 | 5-13  |

| 5.2.1.1  | Subfunction: 00h - Query BIOS Version                | 5-13  |

| 5.2.1.2  | Subfunction: 01h - Query VBE Mode Support            |       |

| 5.2.1.3  | Subfunction: 02h - Set VBE Mode for Second View      | 5-14  |

| 5.2.1.4  | Subfunction: 03h - Enable Second View Mode           | 5-14  |

| 5.2.1.5  | Subfunction: 04h - Disable Second View Mode          | 5-14  |

| 5.2.2    | Standard VGA BIOS Functions                          | 5-15  |

| 5.2.2.1  | Function: 00h - Set Video Mode                       | 5-15  |

| 5.2.2.2  | Function: 01h - Set Cursor Type                      | 5-16  |

| 5.2.2.3  | Function: 02h - Set Cursor Position                  | 5-17  |

| 5.2.2.4  | Function: 03h - Get Cursor Position                  |       |

| 5.2.2.5  | Function: 04h - Light Pen (Not Supported)            | 5-18  |

| 5.2.2.6  | Function: 05h - Select Active Display Page           | 5-18  |

| 5.2.2.7  | Function: 06h - Window Scroll Up                     | 5-19  |

| 5.2.2.8  | Function: 07h - Window Scroll Down                   | 5-19  |

| 5.2.2.9  | Function: 08h - Read Character/Attribute at Cursor   | 5-20  |

| 5.2.2.10 | Function: 09h - Write Character/Attribute at Cursor  | 5-21  |

| 5.2.2.11 | Function: 0Ah - Write Character at Cursor Position   | 5-22  |

| 5.2.2.12 | Function: 0Bh - Background/Border, Palette           |       |

| 5.2.2.13 | Function: 0Ch - Write Dot (Pixel)                    | 5-24  |

| 5.2.2.14 | Function: 0Dh - Read Dot (Pixel)                     |       |

| 5.2.2.15 | Function: 0Eh - Write Character to RAM in TTY Mode   | 5-25  |

| 5.2.2.16 | Function: 0Fh - Get Video State                      |       |

| 5.2.2.17 | Function: 10h - Palette Register (Subfunctions)      | 5-26  |

| 5.2.2.18 | Function: 11h - Character Generation (Subfunctions). |       |

| 5.2.2.19 | Function: 12h - Alternate Select (Subfunctions)      |       |

| 5.2.2.20 | Function: 13h - Write Teletype String                |       |

| 5.2.2.21 | Function: 1Ah - Get/Set Display Combination Code     |       |

| 5.2.2.22 | Function: 1Bh - Collection of Video Information      |       |

| 5.2.2.23 | Function: 1Ch - Video State Information              | 5-64  |

| 5.3      | VESA VBE BIOS Functions                              | 5-66 |

|----------|------------------------------------------------------|------|

| 5.3.1    | Overview                                             | 5-66 |

| 5.3.2    | DDC Implementation                                   | 5-66 |

| 5.3.2.1  | VBE Mode Numbers                                     | 5-67 |

| 5.3.2.2  | VBE Functions Call                                   | 5-68 |

| 5.3.2.3  | VBE Return Status                                    | 5-68 |

| 5.3.3    | VESA BIOS Extended Functions (4Fh)                   | 5-69 |

| 5.3.3.1  | Subfunction: 00h - Return VBE Controller Information | 5-69 |

| 5.3.3.2  | Subfunction: 01h - Return VBE Mode Information       | 5-73 |

| 5.3.3.3  | Subfunction: 02h - Set VBE Mode                      | 5-82 |

| 5.3.3.4  | Subfunction: 03h - Return current VBE Mode           | 5-83 |

| 5.3.3.5  | Subfunction: 04h - Save/Restore State                | 5-84 |

| 5.3.3.6  | Subfunction: 05h - Display Window Control            | 5-85 |

| 5.3.3.7  | Subfunction: 06h - Set/Get Logical Scanline Length   | 5-86 |

| 5.3.3.8  | Subfunction: 07h - Set/Get Display Start             | 5-87 |

| 5.3.3.9  | Subfunction: 08h - Set/Get DAC Palette Format        | 5-88 |

| 5.3.3.10 | Subfunction: 09h - Set/Get Palette Data              | 5-89 |

| 5.3.3.11 | Subfunction: 0Ah - VBE Protected Mode Interface      | 5-90 |

| 5.3.4    | VBE Display Power Management Subfunctions(10h)       | 5-93 |

| 5.3.4.1  | Subfunction: 00h - Report VBE/PM Capabilities        | 5-93 |

| 5.3.4.2  | Subfunction: 01h - Set Display Power State           | 5-94 |

| 5.3.4.3  | Subfunction: 02h - Get Display Power State           | 5-95 |

| 5.3.5    | VBE Display Identification (DDC) Subfunctions(15h)   | 5-96 |

| 5.3.5.1  | Subfunction: 00h - Report VBE/DDC Capabilities       | 5-96 |

| 5.3.5.2  | Subfunction: 01h - Read EDID                         | 5-97 |

| 5.3.6    | VBE / Flat Panel Subfunctions (11h)                  | 5-98 |

| 5.3.6.1  | Flat Panel Interface Functions                       | 5-98 |

| 5.3.6.2  | VBE/FP Completion Codes                              | 5-99 |

| 5.3.6.3  | Subfunction 00h - Panel Extensions Support 5-        | -100 |

| 5.3.6.4  | Subfunction 01h - Return Flat Panel Info 5-          | -102 |

| 5.3.6.5  | Subfunction 03h - Panel Shading Options 5-           | -104 |

| 5.3.6.6  | Subfunction 06h - Vertical & Horizontal Position 5-  | -105 |

| 5.3.6.7  | Subfunction 07h - Vertical & Horizontal Expansion 5- | -107 |

| 5.4      | BIOS Data Area Assignments5-                         | -109 |

| 6       | Programmer's Reference                         |      |

|---------|------------------------------------------------|------|

| 6.1     | Overview                                       | 6-2  |

| 6.2     | Address Mapping                                | 6-2  |

| 6.2.1   | Local Memory Address Space                     | 6-3  |

| 6.2.2   | Memory-Mapped Resources Address Space          | 6-5  |

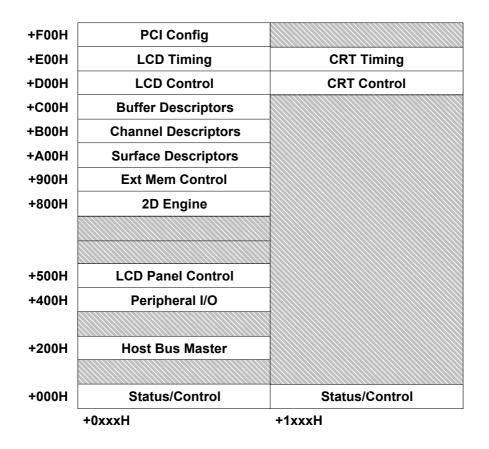

| 6.2.3   | Control Address Space Memory Mapping           | 6-6  |

| 6.2.3.1 | 2D Control Registers (Display 0/Display 1)     | 6-7  |

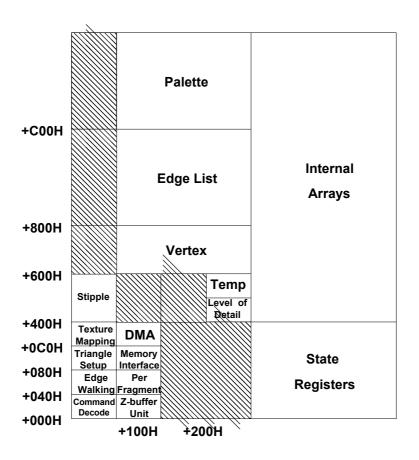

| 6.2.3.2 | 3D Control Registers                           | 6-8  |

| 6.2.3.3 | 3D Command/Parameter FIFO                      | 6-9  |

| 6.2.3.4 | 2D Command/Parameter FIFO                      | 6-9  |

| 6.2.3.5 | 2D Image Data FIFO                             | 6-9  |

| 6.2.4   | Display Memory Arrays                          | 6-10 |

| 6.2.4.1 | Surfaces                                       | 6-10 |

| 6.2.4.2 | Texture Memory                                 | 6-10 |

| 6.2.4.3 | Z-Buffers                                      | 6-10 |

| 6.2.4.4 | Memory Buffer Allocation                       | 6-10 |

| 6.2.5   | Byte Ordering                                  | 6-11 |

| 6.3     | BIOS Functions                                 |      |

| 6.3.1   | BIOS Initialization: Power-On Self Test (POST) | 6-12 |

| 6.3.2   | Set Mode                                       | 6-14 |

| 6.4     | Driver Functions                               | 6-15 |

| 6.4.1   | Device detection                               | 6-15 |

| 6.4.2   | Device configuration                           | 6-16 |

| 6.4.3   | Memory-mapped control address                  |      |

| 6.4.3.1 | Enable/Disable access                          |      |

| 6.4.3.2 | 2D Command Port selector                       | 6-18 |

| 6.4.3.3 | 2D Image Data Port selector                    |      |

| 6.4.3.4 | VGA I/O Ports                                  |      |

| 6.4.3.5 | A0000H-based 128K VGA memory                   |      |

| 6.4.3.6 | PCI configuration space                        |      |

| 6.4.4   | Memory Address Allocation                      |      |

| 6.4.4.1 | Local memory address space                     |      |

| 6.4.4.2 | Display (video) memory address                 |      |

| 6.4.4.3 | 16-bit Real Mode Addressing                    |      |

| 6.4.4.4 | 16-bit Protected Mode Addressing               |      |

| 6.4.4.5 | 32-bit Mode Addressing                         | 6-24 |

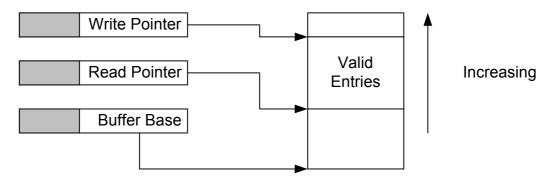

| 6.4.5    | Physical Buffers for FIFOs                        | -26 |

|----------|---------------------------------------------------|-----|

| 6.4.6    | Linear/Segmented mode 6                           | -27 |

| 6.4.7    | Cursor control 6                                  | -28 |

| 6.4.7.1  | Cursor Format 6                                   |     |

| 6.4.7.2  | Cursor data buffer and surface                    |     |

| 6.4.7.3  | Set Monochrome Cursor data                        | -30 |

| 6.4.7.4  | Set Color Cursor data 6                           |     |

| 6.4.7.5  | Cursor Deferred control 6                         |     |

| 6.4.7.6  | Set Cursor Position and Turn Cursor On            | -34 |

| 6.4.8    | lcon                                              | -36 |

| 6.5      | 2D Functions                                      |     |

| 6.5.1    | Display Operations 6                              |     |

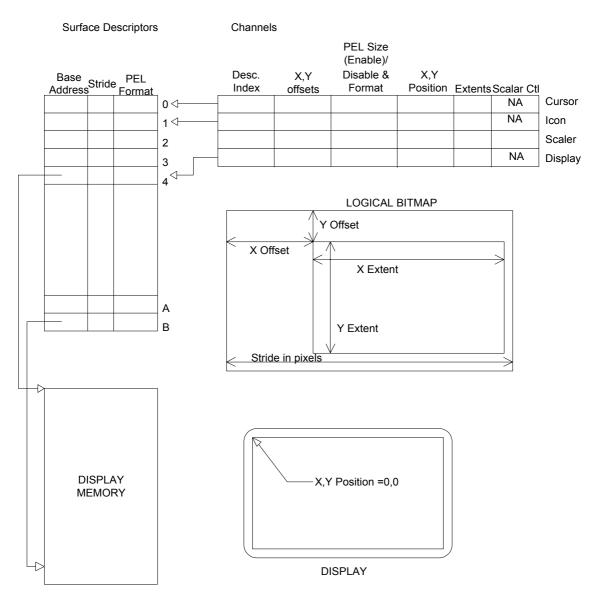

| 6.5.1.1  | Define a Surface 6                                |     |

| 6.5.1.2  | Channel Controls - assign surface                 |     |

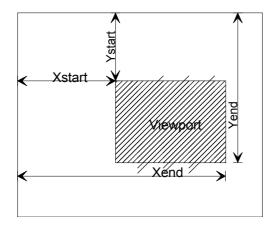

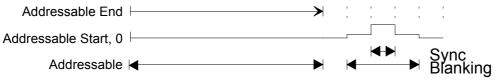

| 6.5.1.3  | Channel Controls - Offsets & viewports location 6 |     |

| 6.5.1.4  | Enable/Disable Channel Display                    |     |

| 6.5.1.5  | Set Display FIFO Controls                         |     |

| 6.5.1.6  | Set Channel 0 X,Y Scale Factors                   |     |

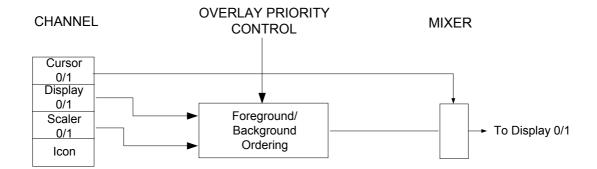

| 6.5.1.7  | Set Overlay Priority 6                            |     |

| 6.5.1.8  | Set Mix Controls - Blend 6                        |     |

| 6.5.1.9  | Set Mix Controls - Color Keying                   |     |

| 6.5.1.10 | Get Displayed Scanline 6                          |     |

| 6.5.2    | 2D Command and Data FIFOs                         | -58 |

| 6.5.2.1  | Image/Data Control Port 6                         |     |

| 6.5.2.2  | 2D Command Port                                   |     |

| 6.5.2.3  | FIFO Status 6                                     | -60 |

| 6.5.3    | 2D Rendering Engine Commands                        |

|----------|-----------------------------------------------------|

| 6.5.3.1  | Wait Engine Idle 6-61                               |

| 6.5.3.2  | Check FIFO size 6-62                                |

| 6.5.3.3  | Clip Rectangle 6-63                                 |

| 6.5.3.4  | Load Mono Pattern 6-64                              |

| 6.5.3.5  | Load Color Pattern 6-64                             |

| 6.5.3.6  | Load General pattern 6-65                           |

| 6.5.3.7  | Block fill (Opaque Rectangle)                       |

| 6.5.3.8  | Transparent Text 6-67                               |

| 6.5.3.9  | Opaque Text 6-68                                    |

| 6.5.3.10 | BitBLT                                              |

| 6.5.3.11 | Pattern BLT Without Source Operand                  |

| 6.5.3.12 | Display Memory Source BLT with/without Pattern 6-71 |

| 6.5.3.13 | System Memory Source BLT with/without Pattern 6-72  |

| 6.5.3.14 | Line Draw                                           |

| 6.6      | 3D Functions                                        |

| 6.6.1    | Overview                                            |

| 6.6.1.1  | Feature Set 6-81                                    |

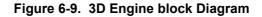

| 6.6.1.2  | 3D Rendering Engine 6-82                            |

| 6.6.1.3  | 3D Rasterization Pipeline                           |

| 6.6.2    | 3D Engine Operation 6-86                            |

| 6.6.2.1  | Initialization 6-86                                 |

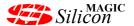

| 6.6.2.2  | 3D Command FIFO 6-88                                |

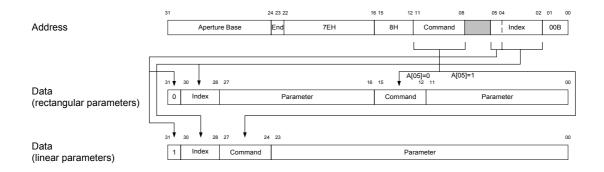

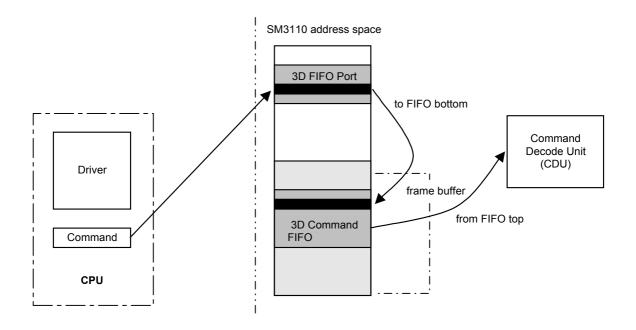

| 6.6.3    | 3D Command Format 6-90                              |

| 6.6.4    | 3D Primitive Commands 6-91                          |

| 6.6.4.1  | Triangle Strip/Fan 6-92                             |

| 6.6.4.2  | Triangle List 6-93                                  |

| 6.6.4.3  | Point List 6-93                                     |

| 6.6.5    | Copy Memory and DMA Command                         |

| 6.6.6    | Synchronization Command 6-96                        |

| 6.6.7    | Load State Register Command                         |

| 6.6.8    | Texture Loading 6-100                               |

| 6.6.9    | 2D/3D synchronization 6-102                         |

| 6.6.10   | Buffer Issues                                       |

| 6.6.10.1 | Buffer Alignment 6-103                              |

| 6.6.10.2 | Buffer Formats                                      |

| 6.6.11   | Performance Issues 6-104                            |

| 6.7      | LCD Panel Programming                  | 6-105 |

|----------|----------------------------------------|-------|

| 6.7.1    | LCD Flat Panel Registers               |       |

| 6.7.1.1  |                                        |       |

| 6.7.1.2  | Set to Desired Mode                    | 6-107 |

| 6.7.1.3  | Standard VGA Modes                     | 6-107 |

| 6.7.1.4  | Enhanced Modes                         | 6-107 |

| 6.7.1.5  | Set Mode Sequence                      | 6-109 |

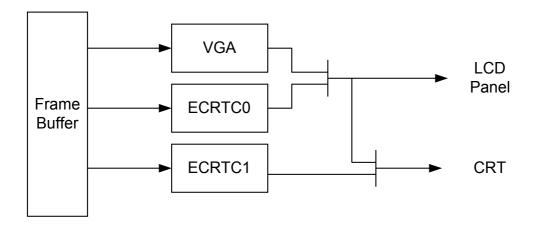

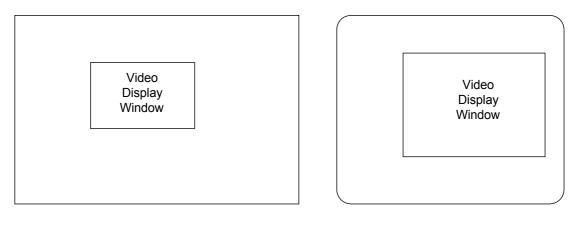

| 6.8      | Dual View                              | 6-110 |

| 6.8.1    | Overview                               | 6-110 |

| 6.8.2    | Enabling Second Display                | 6-110 |

| 6.8.2.1  | Enable Simultaneous View               | 6-111 |

| 6.8.2.2  | Enable Dual View                       | 6-111 |

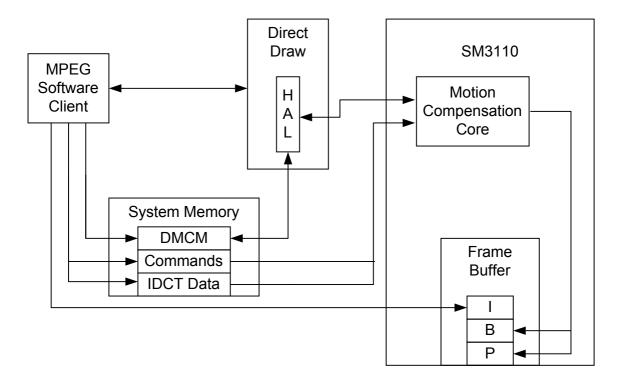

| 6.9      | Motion Compensation                    | 6-112 |

| 6.9.1    | Overview                               | 6-112 |

| 6.9.2    | Block Diagram                          |       |

| 6.9.3    | Motion Compensation Client Commands    | 6-115 |

| 6.9.3.1  | DMCM Commands                          | 6-115 |

| 6.9.3.2  | DMCM surface allocation                | 6-116 |

| 6.9.4    | Registers                              |       |

| 6.9.4.1  | Start and End Decode Functions         | 6-118 |

| 6.9.4.2  | CDU Start Motion Compensation Command  | 6-118 |

| 6.9.4.3  | End of Stream Instruction              | 6-118 |

| 6.9.4.4  | Format Conversion Instruction          | 6-118 |

| 6.9.5    | Display Memory Requirements            | 6-120 |

| 6.9.5.1  | Frame and Format Buffers               | 6-120 |

| 6.9.5.2  | Screen Resolutions Supported           | 6-121 |

| 6.9.5.3  | System Memory Requirements             | 6-121 |

| 6.10     | Power Management                       | 6-122 |

| 6.10.1   | Overview                               | 6-122 |

| 6.10.2   | OnNow Power Management                 | 6-122 |

| 6.10.3   | VESA BIOS Power Management             | 6-122 |

| 6.10.4   | Other Power Management                 | 6-122 |

| 6.10.5   | Registers for OnNow and VESA DPMS      | 6-123 |

| 6.10.5.1 | D0 – On                                | 6-123 |

| 6.10.5.2 | D1 – Standby                           |       |

| 6.10.5.3 | D2 – Suspend                           | 6-124 |

| 6.10.5.4 | D3 – Off                               |       |

| 6.10.6   | Registers for Dynamic Power Management | 6-125 |

| 6.11     | Video Capture                                 |

|----------|-----------------------------------------------|

| 6.11.1   | Overview                                      |

| 6.11.2   | I2C device interface 6-126                    |

| 6.11.3   | Video port control 6-129                      |

| 6.11.4   | Interrupt for video capture 6-13              |

| 6.12     | TV Out                                        |

| 6.13     | Diagnostics                                   |

| 6.14     | Software Definitions 6-133                    |

| 6.14.1   | Equates 6-133                                 |

| 6.14.2   | Macros 6-142                                  |

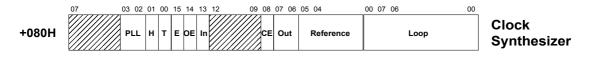

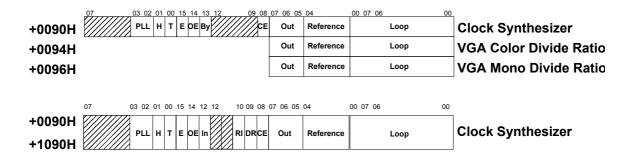

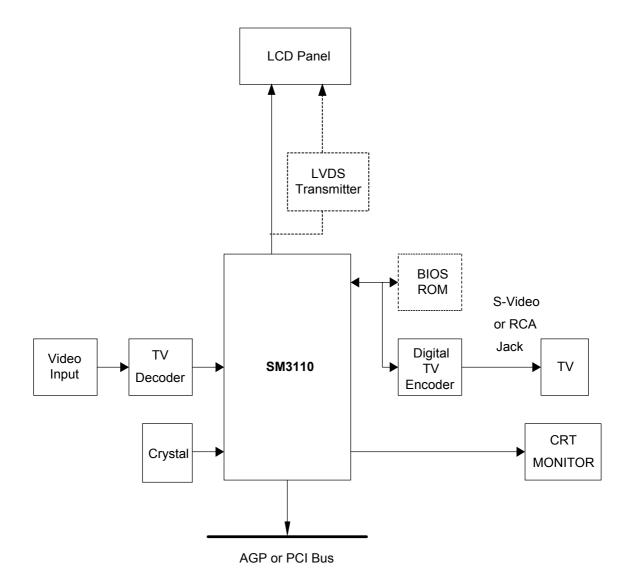

| 6.14.3   | Clock Synthesizer Programming Guide           |

| 6.14.3.1 | Theory of Operation                           |

| 6.14.3.2 | Registers 6-14                                |

| 6.14.3.3 | Memory/Dot/Panel Clock Frequency Control 6-14 |

| 6.14.3.4 | Memory Clock Synthesizer VCO Control 6-146    |

| 6.14.3.5 | Dot/Panel Clock Synthesizer VCO Control 6-147 |

| 6.14.3.6 | Selecting Register Value                      |

| 6.14.3.7 | Programming Limitations                       |

| 6.14.3.8 | Register Values for Common Frequencies 6-149  |

| 7       | Application Notes                        |       |

|---------|------------------------------------------|-------|

| 7.1     | Overview                                 | . 7-2 |

| 7.2     | Board Design                             | . 7-2 |

| 7.2.1   | Power Supply                             | . 7-3 |

| 7.2.2   | Block Diagram                            | . 7-4 |

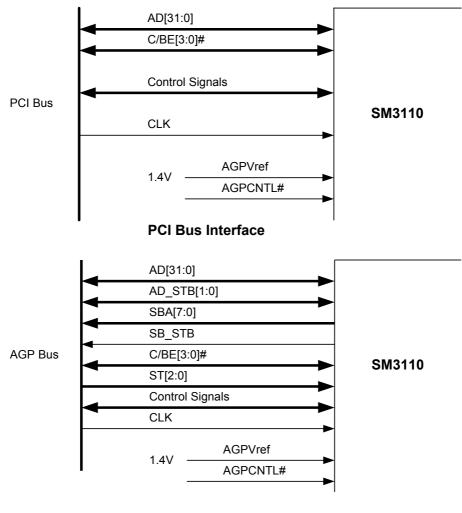

| 7.2.3   | Host Interface                           | . 7-5 |

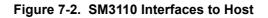

| 7.2.4   | Reference Clock                          | . 7-6 |

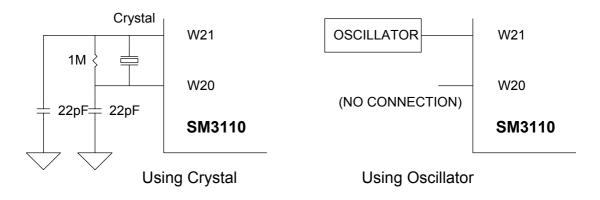

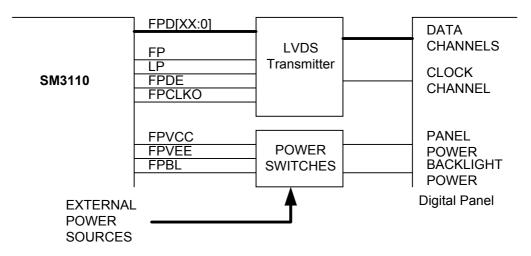

| 7.2.5   | LCD Panel Interface                      | . 7-7 |

| 7.2.6   | LVDS Transmitter Interface               | . 7-8 |

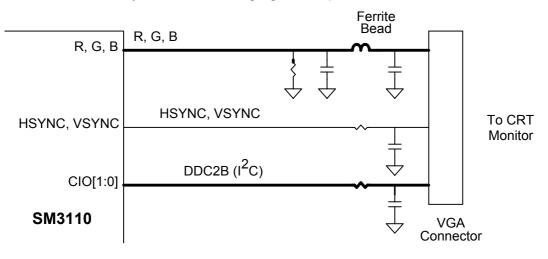

| 7.2.7   | CRT Monitor Interface                    | 7-10  |

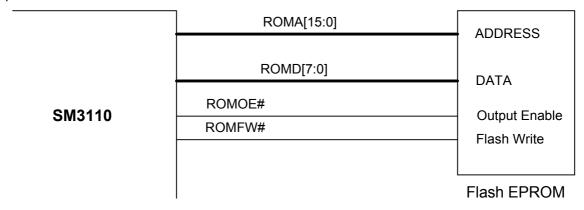

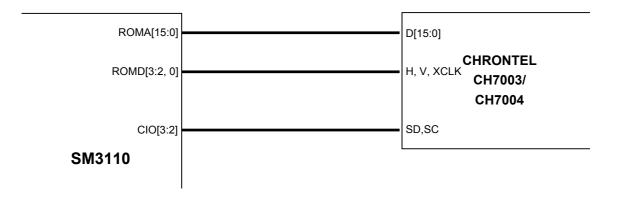

| 7.2.8   | BIOS ROM Interface                       | 7-11  |

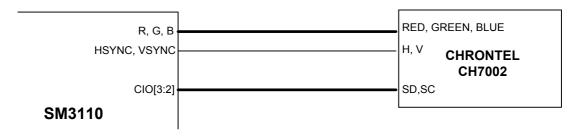

| 7.2.9   | Analog and Digital TV Encoder Interfaces | 7-12  |

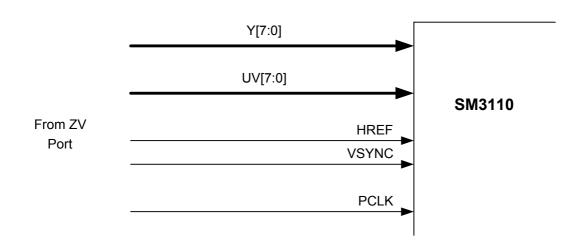

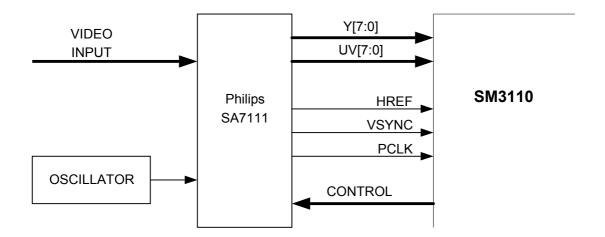

| 7.2.10  | TV Decoder Interface                     | 7-13  |

| 7.3     | Power-On Strapping                       | 7-14  |

| 7.3.1   | Power-on Strapping Pins                  | 7-14  |

| 7.3.2   | Strapping Method                         | 7-15  |

| 7.3.2.1 | External Pull Down Resistor              | 7-15  |

| 7.3.2.2 | Registers                                | 7-15  |

| 7.3.2.3 | Strapping Pin Functions                  | 7-16  |

| 7.4     | Board-level Testing                      | 7-17  |

| 7.4.1   | Test Mode Control Pins                   |       |

| 7.4.2   | Test Modes                               |       |

| 7.5     | Programmable (Peripheral) I/O            | 7-23  |

| 7.5.1   | Customer I/O                             | 7-23  |

| 7.5.1.1 | Customer Pins                            |       |

| 7.5.1.2 | Customer Registers                       |       |

| 7.5.2   | Peripheral I/O                           |       |

| 7.5.2.1 | Peripheral I/O Pins                      |       |

| 7.5.2.2 | Peripheral I/O Registers                 | 7-27  |

| Α     | Appendix A                              |     |

|-------|-----------------------------------------|-----|

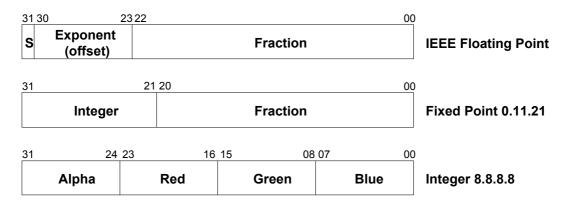

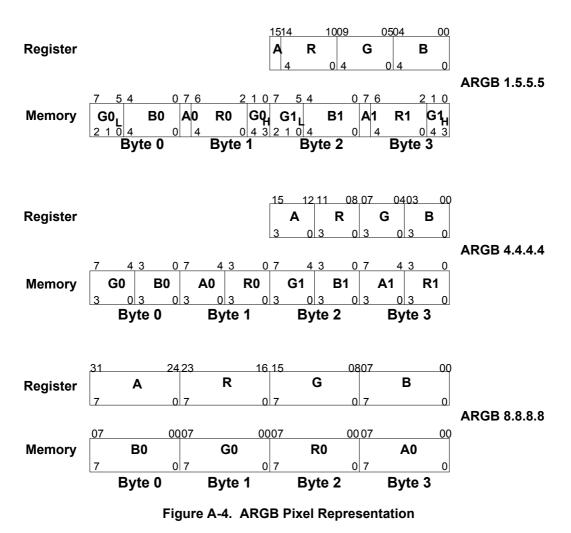

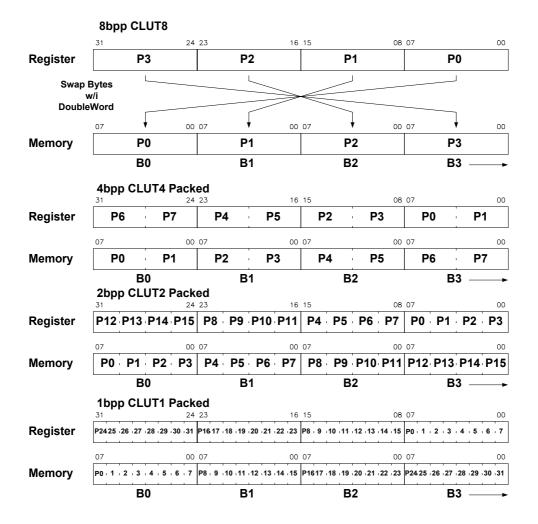

| A.1   | Pixel Format Information                | A-2 |

| A.1.1 | Enhanced Data Format                    | A-2 |

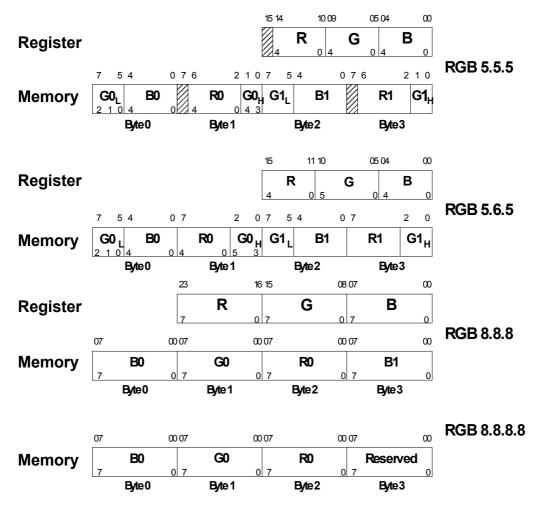

| A.1.2 | RGB Pixel Formats                       | A-3 |

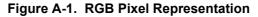

| A.1.3 | Palettized/Color Lookup Table           | A-5 |

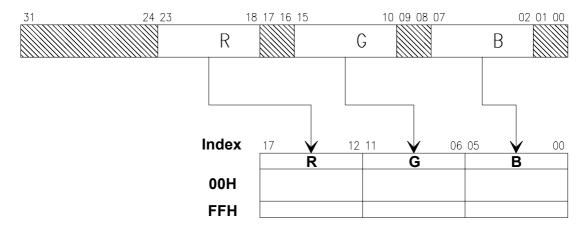

| A.1.4 | CLUT Data Format                        | A-6 |

| A.2   | 3D Data Formats                         | A-7 |

| A.2.1 | Coordinates                             | A-7 |

| A.2.2 | RGB Pixel Formats                       | A-7 |

| A.2.3 | ARGB Pixel Formats                      | A-7 |

| A.2.4 | Texel Formats                           | A-8 |

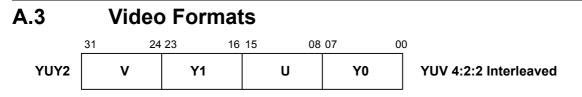

| A.3   | Video FormatsA                          | -10 |

| A.3.1 | Cursor                                  | -11 |

| A.3.2 | VGA Data Formats A                      | -12 |

| A.3.3 | Planar                                  | -13 |

| A.3.4 | Text                                    | -14 |

| A.3.5 | Packed Pixel/Linear A                   | -15 |

| В     | Appendix B                              |     |

| B.1   | Graphics Modes Support                  |     |

| B.1.1 | Video Display Window Memory Constraints |     |

| B.1.2 | Definitions                             |     |

| B.1.3 | Motion Compensation Memory Requirements | B-3 |

| B.2   | Graphics Modes Summary                  |     |

| B.2.1 | Single Display with NTSC Video          |     |

| B.2.2 | Single Display with PAL Video           |     |

| B.2.3 | Dual display with NTSC Video            |     |

| B.2.4 | Dual display with PAL Video             | B-7 |

| С     | Appendix C                              |     |

| C.1   | References                              | C-2 |

1

SM3110 Features Overview

# SM3110 Features Overview

**Features Overview**

# 2D/3D/Video LCD/CRT Graphics Accelerator

#### 4 Mbytes of embedded graphics RAM

#### **Bi/TriLinear MIPmap 3D Engine**

Advanced Floating Point 3D setup engine Z-buffering

**3 Op 2D Engine** 256 ROP on 8, 16, 24 bpp with transparency

#### Video playback acceleration

Color and Chroma key Bi-linear (X,Y) interpolated scaling Color space conversion Motion Compensation Bob and Weave

Industry standard Video input support

ZV port, I<sup>2</sup>C support

MyView<sup>™</sup> dual display support Independent LCD and CRT display

#### LCD panels and CRT support

TFT up to 1280x1024x24 bpp DSTN up to 1280x1024x16bpp CRT up to 1600x1200x16 bpp

AGP 2x and 66 MHz PCI 2.2 host interface with bus mastering

SmartPower<sup>TM</sup> power management system Full VESA 2.0 DPMS and DDC2B support 2.5V and 3.3V operation with 5V tolerant I/O

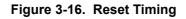

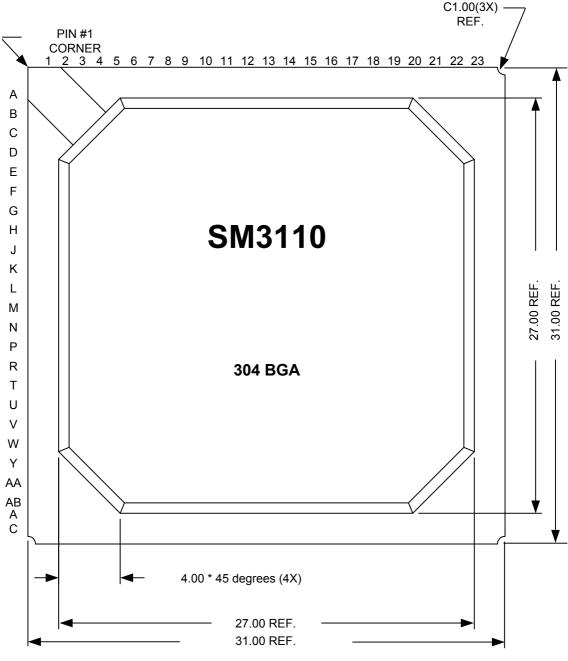

#### 304 pin PBGA package

The SM3110 provides an optimal graphics subsystem for notebook computers. Its unique design embeds rich features and superior performance in a *single chip*.

#### **Embedded Performance and \$avings**

The SM3110 integrates an advanced 3D engine, a robust 3 Op 2D accelerator, hardware video playback acceleration with interpolated scaling, independent dual display channels for LCD and CRT, a true color 230 MHz DAC and 4 Mbytes of embedded DRAM optimized for bandwidth availability and usage.

By integrating the optimal memory and functionality required by popular notebook applications, the SM3110 multimedia solution eliminates two or more external components, while attaining highest possible performance. For notebook computers this all adds up to ease of design and valuable savings in PCB space, weight, and subsystem costs.

Moreover, its SmartPower<sup>TM</sup> power management system ensures ultra-low power consumption during all operations and adheres to the ACPI goals for 1999 mobile computers which adds significant time to notebook battery life.

### **3D Engine**

- Floating point 3D setup engine

- Trilinear MIPmapping

- Bilinear filtering

- True divide-per-pixel perspective correction

- 16-bit Z-buffer support

- Alpha blending

- Transparency

- Texture blending

- Colored fog

- Specular lighting

- Gouraud shading

- Logical OP, dithering

- Stipple support

- On-chip texture palette

- Supports 8, 16 or 32 bpp

- 1, 2, 4, 8, 16 bit texture map support

- Up to 1M Byte Command/Parameter buffer

### Embedded 4M Bytes DRAM

Embedded DRAM configurable for display buffers, Z-buffers, texture buffers or command buffers

### 2D Engine

- 3 OP bitBLT engine

- 256 ROP

- Color expansion

- Clipping

- Mono/Color pattern fill

- Opaque rectangle

- Transparent text

- Opaque text

- Color compare for color keying/transparency control

- 8, 16, 24bpp color

- Frame synchronization

- 32KB data FIFO

- 32KB command FIFO

- 256x256 monochrome or 32x32 color hardware cursor

### **High-performance AGP Interface**

- AGP 2.0 interface, 1x and 2x with Sideband addressing

- 32-bit, 66MHz PCI 2.2 interface

- DMA bus mastering

- Linear addressable frame buffer

- Bi-endian data format support

- 3.3V host interface with 5V tolerance

### Video Playback Acceleration

- Hardware destination color and chroma key support

- Colorspace conversion

- Motion compensation to ensure >30fps during MPEG/DVD playback

- Bob and weave

- Bi-linear (X, Y) interpolated scaling

- Independently scalable hardware windows for each display channel

- YUV-RGB conversion (4:2:2 -> CLUT8, 555, 565, 888)

### Industry Standard Video Input

- ZV port

- I<sup>2</sup>C support

- Glueless interface to video digitizers

- Real-time 720x525 video capture

- On-the-fly horizontal downscaling

# SmartPower<sup>TM</sup> = longer battery life

- Ultra-low power consumption achieved with dynamic control during all operations

- Comprehensive support for suspend, standby and hibernation modes

- VESA DPMS 2.0 and DDC2B support for both GreenPC and CRT Plugand-play

- 2.5V internal operation, 3.3V I/O with 5V tolerance

#### Display Output MyView<sup>TM</sup> dual display support

- Allows true multitasking by displaying

- different images on LCD and CRT simultaneously

- Independent resolution and refresh rate for each display for optimal display quality

#### High resolution support up to 1600x1200 CRT

- DSTN up to 1280x1024x16bpp

- CRT up to 1600x1200x16bpp

# True color 230MHz palette DAC with gamma correction

- 4, 8, 16, 24, 32bpp support up to 1600x1200 resolution at 85Hz

- DDC2B support

# DSTN, TFT flat panel support with gamma correction

- OEM-customizable Hardware Display Icon

- 9, 12, 18, 24 bpp TFT LCD panel support with dithering in resolutions up to 1280x1024 at 85Hz

- 8, 16, 24 bit DSTN with dithering and FRC support in resolutions up to 1280x1024 at 85Hz

- 12, 18, 24 and 36-bit panel interface

- 3,4,6 and 8-bit dithering support

- VGA mode LCD scaling and centering support

- Automatic panel power sequence control

- Fast shutdown for Hot-Battery-Switching

- Configurable default display at power-up

- Two independent hardware cursors

### LVDS or TMDS Interface

#### Digital or Analog TV encoder interface

# Maximum display resolutions supported

| Mode                                    |                  | Resolution (w pixels x h pixels) x<br>Color Depth (bits/pixel) |  |  |  |

|-----------------------------------------|------------------|----------------------------------------------------------------|--|--|--|

| Single Display                          | CRT              | 1600 x 1200 x 16                                               |  |  |  |

|                                         | CRT or TFT       | 1280 x 1024 x 24                                               |  |  |  |

|                                         | DSTN             | 1280 x 1024 x 16                                               |  |  |  |

|                                         | CRT or LCD       | CRT or LCD         1024 x 768 x 32                             |  |  |  |

| Single Display w/NTSC DVD (full-screen) | CRT or LCD       | 640 x 480 x 24                                                 |  |  |  |

| MyView <sup>™</sup> Dual Displays       | LCD              | CRT                                                            |  |  |  |

|                                         | 1280 x 1024 x 16 | 800 x 600 x 16                                                 |  |  |  |

|                                         | 1280 x 1024 x 8  | 1600 x 1200 x 8                                                |  |  |  |

|                                         | 1024 x 768 x 24  | 800 x 600 x 24                                                 |  |  |  |

|                                         | 1024 x 768 x 16  | 1024 x 768 x 16                                                |  |  |  |

|                                         | 1024 x 768 x 8   | 1600 x 1200 x 8                                                |  |  |  |

|                                         | 800 x 600 x 32   | 800 x 600 x 32                                                 |  |  |  |

# **Optimized drivers, BIOS and utilities**

The SM3110 is designed to accelerate Microsoft's DirectX architecture including DirectDraw and Direct3D, plus OpenGL in the Windows environment. Optimized drivers and utilities for Windows 95/98, NT 4.0, and Windows 2000 operating systems back the high performance hardware. An ICD driver for OpenGL is also available.

The SM3110 is supported by the industry standard VESA VBE-compliant VGA BIOS to provide optimum performance and functionality in VGA and VESA extended display modes.

The SM3110 is backed by a strong suite of utilities to help with the customization and update of BIOS. A utility to generate and fine tune the timing configuration of LCD panels in the BIOS is also available.

| Software Drivers               | Resolutions Supported                | No. of colors |  |

|--------------------------------|--------------------------------------|---------------|--|

| Microsoft Windows 95, 98,      | 640x480, 720x480, 800x600,           | 256 or        |  |

| 2000, NT 4.0, Direct3D, OpenGL | 1024x768, 1280x1024, 1600x1200       | 65536         |  |

|                                | 640x480, 720x480, 800x600, 1024x768, | 16.8 million  |  |

|                                | 1280x1024                            |               |  |

| Microsoft WDM/VPE/VPM Driver   | Resolution-independent               | -             |  |

| DVD Playback                   | 800x600                              | 65536         |  |

|                                | 640x480                              | 16.8 million  |  |

Trademarks are the property of their respective holders.

Architecture Overview

# 2 Architecture Overview

2.1 System Configuration

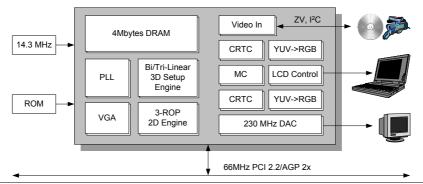

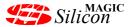

#### Figure 2-1. Typical SM3110 System Configuration

The SM3110 is an integrated graphics accelerator designed for high performance in a limited space environment, such as a laptop computer. The SM3110 Graphics Accelerator has a number of interfaces to accommodate a variety of configurations and devices.

The host interface is glueless for a direct connection to either AGP or PCI buses. A Zoom Video input port (ZV Port) is provided to accept live video. A single external crystal supplies reference clock timing to three internal independently programmable Phase Locked Loops (PLL). The BIOS ROM port can access a separate graphics ROM or it can be converted for output to a digital TV encoder if the graphics ROM is not used in the system. The display outputs can drive a DSTN or TFT panel and a CRT monitor simultaneously. The data on two displays can be either the same or different, providing a flexible system configuration. Either display port can connect to a TV encoder for TV display. The DAC and clock synthesizers are also built in to minimize the need for external components.

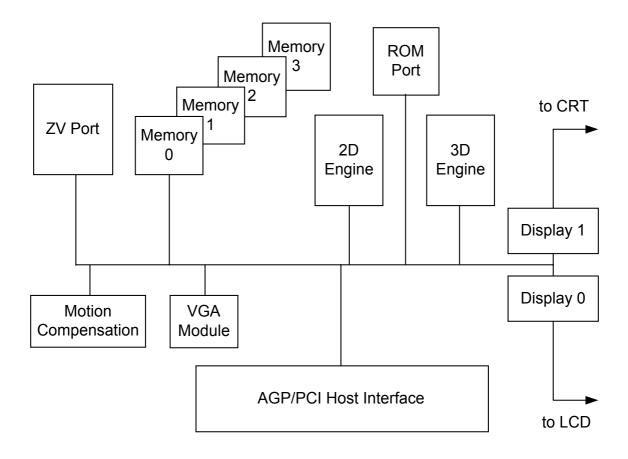

2.2 Internal Configuration

Figure 2-2. SM3110 Internal View

The architecture consists of a host interface, a standard VGA module, a Zoom Video port, a ROM port, four 1MB modules of high performance embedded memory, a 2D engine, a 3D engine, a motion compensation module for accelerating MPEG-2 playback and sophisticated dual display circuitry to support single/simultaneous/dual display on any LCD panel/CRT monitor/TV combination.

The SM3110 has a glueless system interface that is compliant with PCI Local Bus, Revision 2.2 and supports Intel's Accelerated Graphics Port (AGP), Revision 2.0. The system interface can initiate bus transactions as a master and supports 5V and 3.3V signaling and 66 MHz operation. It supports PCI Bus Power Management Interface for ACPI compliant power management. AGP support includes AGP 1x and 2x with Local Texturing, AGP Pipelining, AGP Sideband Addressing, and AGP Frame Mode.

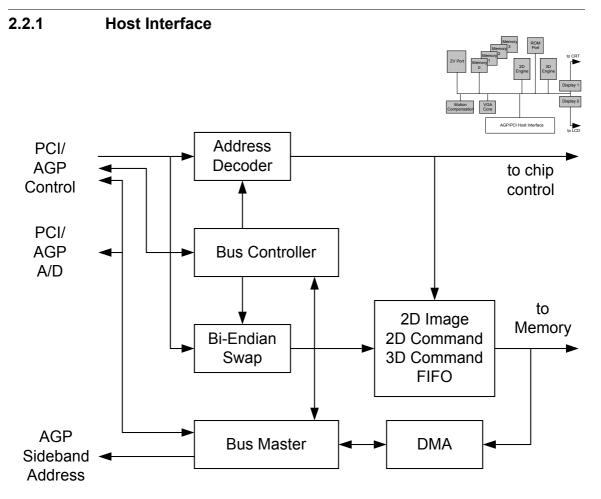

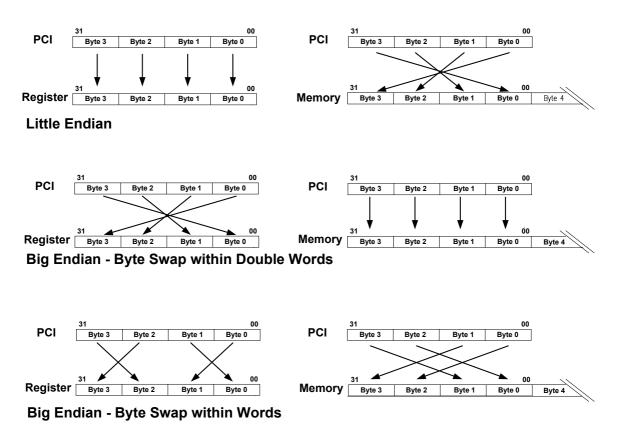

The host interface supports bi-endian data formats. It has 2D and 3D command/data buffers to improve bus throughput. It handles DMA in bus master mode to improve data transfer while leaving the CPU free for other tasks. In AGP configuration the host interface also supports sideband addressing for higher data throughput.

Embedded Memory

2.2.2

# AGP/PCI Host In DRAM Module 1 Megabyte Embedded DRAM DRAM Control 3D 2D 3D Read 2D Read Texture Write Write Buffer Buffer Cache Buffer Buffer 3D Read Bus 2D Read Bus 3D Write Bus 2D Write Bus Texture Data

The SM3110 includes 4 megabytes of embedded memory. Four memory modules of 1 megabyte each comprise the internal memory. The modules have separate read and write buffers for the 2D and 3D data buses and one buffer for texture cache. When combined, the interface to internal memory provides over 6.4 gigabytes/second peak memory bandwidth.

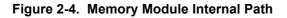

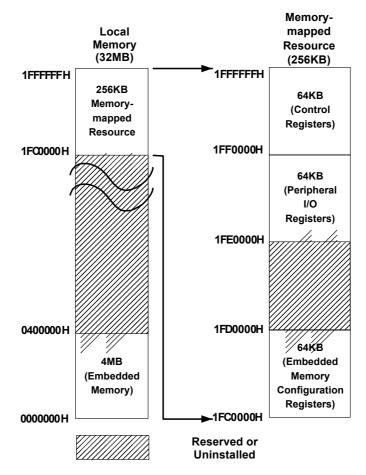

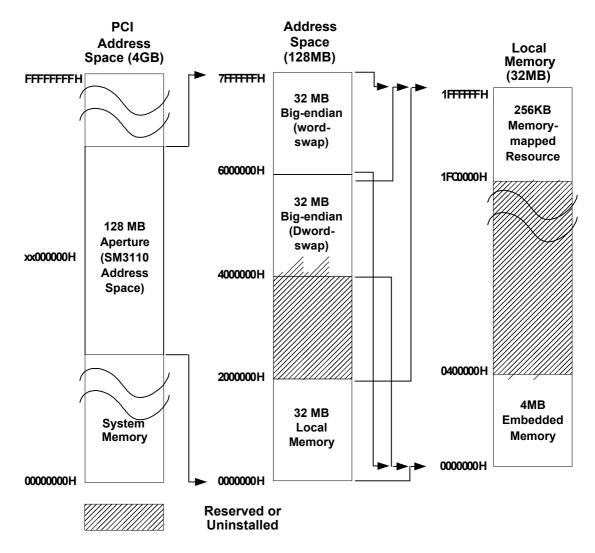

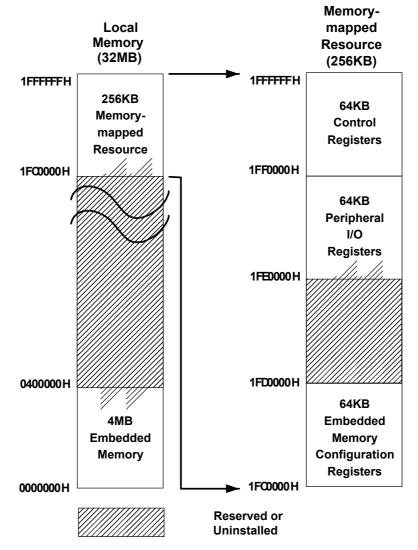

The SM3110 claims 128MB of memory space through AGP/PCI configuration. This 128 megabytes is divided into 4 contiguous 32MB address ranges. The lowest 32MB is for little endian data. The next 32MB is reserved. The swap byte within doubleword big endian copy occupies the next 32MB and the swap bytes within word big endian copy occupies the highest 32MB. The last 256KB of each 32MB address range is reserved for 2D and 3D control accesses.

|                |         |               |           | Big Endian | Big Endian  |

|----------------|---------|---------------|-----------|------------|-------------|

|                |         |               |           | (Double-   |             |

|                |         | Little Endian | Reserved  | Word Swap) | (Word Swap) |

| Range          | Size    | Base          | Base      | Base       | Base        |

| Display Memory | 31.75MB | 00000000H     | 02000000H | 04000000H  | 0600000H    |

| Control        | 0.25MB  | 01FC0000H     | 03FC0000H | 05FC0000H  | 07FC0000H   |

| Total          | 32.00MB |               |           |            |             |

#### Table 2-1. Local Address Space Allocation

Besides the memory address mentioned above, SM3110 also provides access to register I/O and 128KB memory at 000A0000H address space for compatibility with standard VGA. Larger physical memory available in super VGA configuration is made accessible via an I/O addressed bank offset register.

Figure 2-5. Address Space Allocation

# 2.2.3 VGA Module AGP/PCI Host address MUX data CRTC to memory Graphics Controller Sequencer Attribute Controller Display Subsystem

SM3110 has a VGA core fully compatible with the industry-standard IBM VGA adapter. This module provides direct access logic to the frame buffer and supports all functions performed by the Sequencer and VGA Graphics Controller registers. Standard VESA and VGA display timings are also provided by this module.

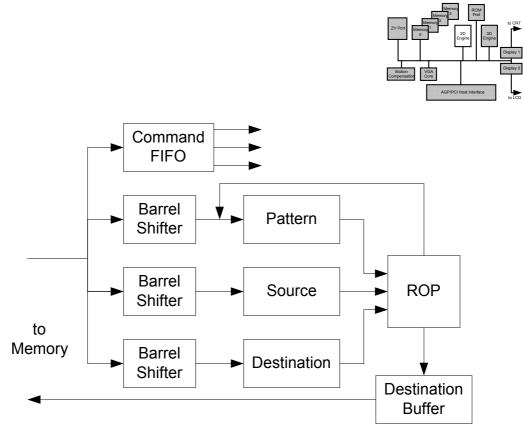

2.2.4 2D Rendering Engine

Figure 2-7. 2D BitBLT Engine Internal Data Path

The SM3110 has a high performance 2D bitBLT engine. The 2D engine has a three-operand raster operations (ROP) engine supporting linear and rectangular addressing which is fully Microsoft Windows compatible. It also supports screen-to-screen or memory-to-screen bitBLT with color expansion and transparency control.

The 2D command FIFO receives and decodes commands buffered for the 2D engine. Separate source data, destination data and pattern buffers have their own shifters to align data before they are fed into the ROP unit. A destination buffer stores the results before writing back to the frame buffer for optimized performance in both the 2D engine and the memory interface. This engine also provides transparency, color expansion and color keying during the bitBLT operation.

# Architecture Overview

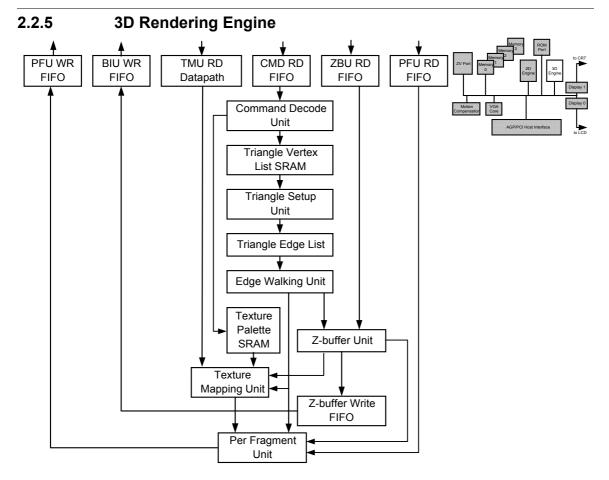

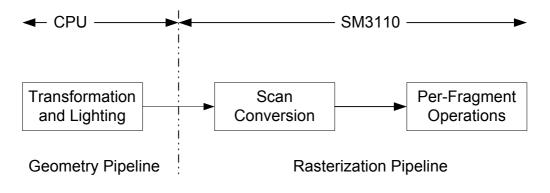

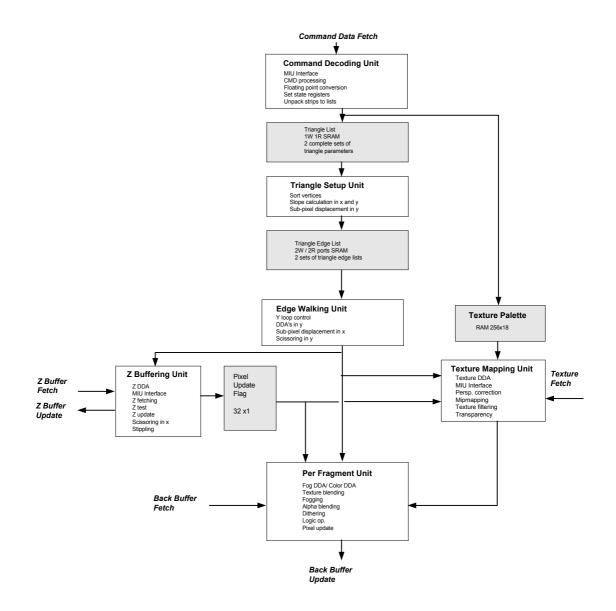

Figure 2-8. 3D Engine Internal Data Path

The SM3110 has a multi-stage 3D rendering engine. It is a one-cycle, bilinear, perspective corrected and two-cycle, trilinear, texture-mapped, perspective corrected MIPmap texture calculation engine. The major components of this rendering engine include a command unit, a triangle setup engine, a texture mapping unit, a texture cache buffer, a texture palette, a per fragment unit and a 16-bit Z-buffer.

The command unit provides command decoding and control of the engine. The triangle setup engine speeds up calculations in the setup process by getting setup information from the host and performing the necessary calculations, freeing the host CPU for other tasks. The texture unit calculates correct texels for each pixel with a bilinear or trilinear MIPmapped filter and perspective correction. The texture palette converts indexed color into 16-bit color. The Z-buffer unit calculates Z value of each new pixel and compares against the Z value in the frame buffer for accurate hidden surface removal. The rendering engine renders each pixel using lighting, fogging, specular highlighting and texturing functions to generate realistic images at a high frame rate.

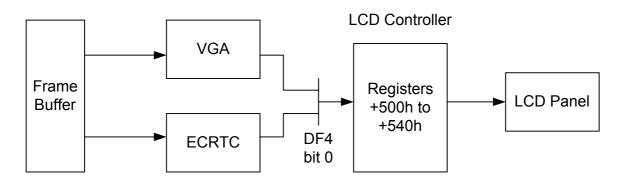

**Display Pipeline** 2.2.6 MEMORY Enhanced CRTC 1 AGP/PCI Host In VIDEO CURSOR SCALER FIFO RAM DISPLAY PIXEL CLUT CURSOR MIXING/ FIFO UNPACK GAMMA KEYING OVERLAY CRT DAC CORREC **DISPLAY 1** MEMORY Enhanced CRTC 0 VIDEO CURSOR SCALER RAM FIFO DISPLAY PIXEL DITHER MIXING/ CURSOR CLUT GAMMA FIFO UNPACK LCD KEYING OVERLAY CORREC /FRC VGA LVDS/ PaneLink ICON MEMORY **DISPLAY 0**

Figure 2-9. Display Pipeline

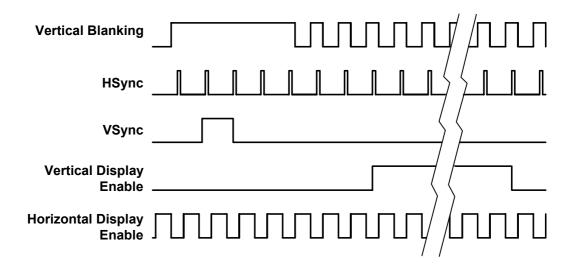

The display subsystem has two independent display pipelines. Each pipeline has its own enhanced CRT controller (CRTC), display FIFO, video FIFO, pixel unpacking circuit, color lookup table (CLUT), color keying circuit and scaler. Display 0 supports all standard VGA functions including all standard VESA display modes. Both displays support extended VESA modes for higher visual quality. The two enhanced CRT controllers can be set to display different data with different resolutions and refresh rates. Display 1 can accept display 0 data through a multiplexing circuit.

# Architecture Overview

The last stages of the two pipelines differ somewhat. Display pipeline 0 is optimized for flat panel display with gamma correction. It has a software selectable dithering and Frame Rate Control (FRC) circuit to improve display quality on LCD panels. The same interface can also provide digital data to drive an external LVDS/PaneLink transmitter. It supports 8, 16, 24 and 36 pin interface DSTN panels with dithering and FRC. It also supports a 9, 12, 18, 24 and 36 pin interface TFT panels with dithering, and supports scaling and centering if the display resolution is lower than panel resolution. SM3110 also supports panning if the display resolution is larger than the panel resolution.

Display pipeline 1 integrates a true color 230 MHz palette DAC with gamma correction. It can display 4, 8, 15, 16, 24 and 32 bits per pixel (bpp) with standard VGA, VESA and programmable enhanced display formats up to 1600 by 1200 resolution at 85Hz. VESA Display Power Management Signaling 1.0 (DPMS 1.0) is supported for power management. The SM3110 also supports VESA Display Data Channel 2.0/2.0B (DDC2/DDC2B) for monitor Plug & Play support. The CRT can have display timing and control independent of the flat panel for dual independent displays.

The display subsystem supports two hardware cursors and a hardware icon. The size of both the cursors and icon is 32 pixels by 32 pixels in 8bpp color mode or 256 pixels by 256 pixels in monochrome mode. The cursors can be on both display pipelines, while the icon can only be on the display 0 pipeline.

2.2.7 Video Input

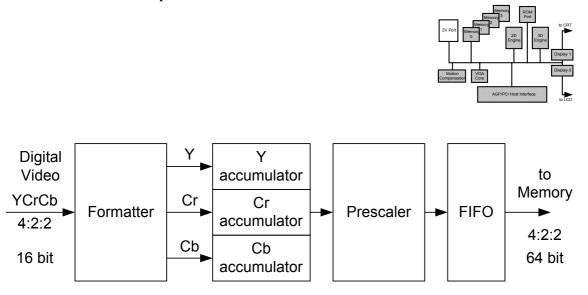

Figure 2-10. Video Input

The SM3110 supports PCMCIA Zoomed Video (ZV) Port and direct video input of ITU-R BT. 601 compliant YCrCb 4:2:2 digital video data.

The video data from this port is first pixel-aligned by a formatter and put into an accumulator. When two complete pixels are accumulated, the decimator circuit prescales the data and writes the scaled result into the frame buffer through its own FIFO for video capture.

# Architecture Overview

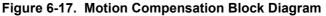

### 2.2.8 Motion Compensation

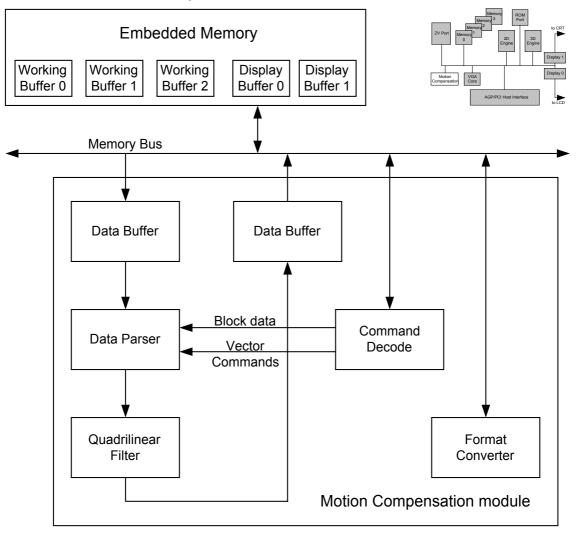

Figure 2-11. Motion Compensation Subsystem

The motion compensation subsystem consists of the motion compensation module and five buffers residing in internal memory. The motion compensation module accepts enhanced MPEG-2 video data, parses the macroblock data and applies the quadrilinear filter. The resulting picture is assembled in the working buffers and then converted on the fly from the input 4:2:0 YCrCb format to output 4:2:2 YCrCb format and written to the display buffer.

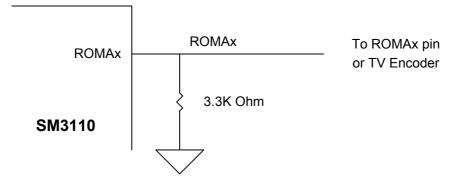

### 2.2.9 ROM Port

The SM3110 supports external display BIOS ROM in standard VGA BIOS address 0xC000:0000. The ROM can be EPROM, EEPROM, or flash ROM. The size is either 32KB or 64KB and is set by power-on strapping.

If display BIOS is incorporated in system BIOS, this port can be converted to drive an external digital TV encoder. The image can be programmed to be the same as either the CRT or the panel display.

The ROM port can also be used for any 8-bit peripheral I/O function through the peripheral port at address offset +1FE0000H.

# 2.3 Additional Features

### 2.3.1 Power Management

The SM3110 supports PCI Bus Power Management Interface for ACPI compliant power management, VESA Display Power Management Signaling 1.0 (DPMS 1.0) and VESA Display Data Channel 2.0/2.0B (DDC2/DDC2B) for monitor Plug & Play support.

The panel interface, DAC, 2D engine, 3D engine, both scalers and the entire display 1 (CRT) pipeline can be turned off individually to tailor the chip configuration for the lowest power consumption. The SM3110 allows the lowest possible power use dynamically through driver/register-level control for the task at hand.

# 2.3.2 Board-level Test Functions

The SM3110 has build-in test functions to perform open/short connection testing to help in detecting manufacturing problems. This simple, effective method allows quick detection of any shorted connections or failed soldering. SM3110 also has an isolation test function which allows the board to be tested without response from the SM3110.

### 2.3.3 Clocks

The SM3110 has 3 internal clock synthesizers which provide a wide range of frequencies to the memory clock and the two display clocks. The inputs of the synthesizers are from a single clock source, which can be an oscillator or a crystal. The typical frequency is 14.31818 MHz.

# 2.3.4 Inter-IC (I<sup>2</sup>C) Interface

The SM3110 has 8 programmable bi-directional pins to support I<sup>2</sup>C and other control functions. Two sets of pins are provided to support DDC2B monitor control and a TV decoder/encoder for video in/TV out functions. More channels can be provided if the need arises.

# 3.1 Pin Descriptions

### 3.1.1 AGP/PCI Interface

Note: For detailed pin description, please refer to AGP Spec. 2.0 and PCI Spec. 2.2.

|             |                             | *Input/ |                                         |

|-------------|-----------------------------|---------|-----------------------------------------|

| Signal Name | Pin #                       | Output  | •                                       |

| AD_STB[1:0] | AC11, AC20                  | I5/O2   | AD bus strobe                           |

| AD[31:0]    | AC8, Y9, AC9, AA9, AB10,    | 15/02   | AD bus                                  |

|             | Y10, AC10, Y11, AB12, Y13,  |         |                                         |

|             | AC12, AA13, AC13, Y14,      |         |                                         |

|             | AB14, Y15, Y18, AC17, Y19,  |         |                                         |

|             | AB18, AA19, AC18, Y20,      |         |                                         |

|             | AB19, AC21, Y21, AC22, Y23, |         |                                         |

|             | AB22, AA23, AC23, AB23      | 15/00   | Due Ouwerstand Data Frickle             |

| C/BE[3:0]#  | AA12, AC14, AC16, AA20      | 15/02   | Bus Command and Byte Enable             |

| CLKRUN#     | AB2                         | 15/02   | Clock start request                     |

| DEVSEL#     | AB16                        | 15/02   | Device Select                           |

| FRAME#      | AA15                        | I5/O2   | Cycle Frame (PCI only)                  |

| GNT#        | Y5                          | I5/O2   | Bus request Granted                     |

| IDSEL       | AA11                        | I5/O2   | Initialization Device Select (PCI only) |

| INTA#       | AC1                         | 15/02   | Interrupt request A                     |

| IRDY#       | AC15                        | 15/02   | Initiator Ready                         |

| TRDY#       | Y16                         | 15/02   | Target Ready                            |

| STOP#       | AA16                        | 15/02   | Stop                                    |

| M66EN       | AC19                        | 15/02   | 66MHz Enable                            |

| PAR         | AA17                        | 15/02   | Parity                                  |

| RBF#        | AC4                         | 15/02   | Read Buffer Full                        |

| REQ#        | AC2                         | 15/02   | Bus Request                             |

| RST#        | AA4                         | I5/O2   | System Reset                            |

| SB_STB      | AC6                         | I5/O2   | SideBand Address Strobe                 |

| SBA[7:0]    | AA8, AB8, Y8, AC7, Y7, AB6, | I5/O2   | SideBand Address Bus                    |

|             | Y6, AC5                     |         |                                         |

| CLK         | Y4                          | 15/02   | System Clock                            |

| ST[2:0]     | AB4, AA5, AC3               | I5/O2   | Status Bus                              |

| AGPCNTL#    | AA1                         | 12      | AGP Pad Power Control. This is not      |

|             |                             |         | part of AGP bus signal.                 |

| AGPVref     | Y22                         | AI      | AGP Pad voltage reference input.        |

|             |                             |         | This is part of Silicon Magic's AGP     |

|             |                             |         | power management.                       |

\*See Pad Description, Section 3.1.12

## 3.1.2 Panel Interface

| Signal     |                            |       | Alternate |                                  |

|------------|----------------------------|-------|-----------|----------------------------------|

| Name       | Pin #                      | I/O*  | Function  | Description                      |

| FPCLKO     | D13                        | I6/O5 |           | Clock Output to Flat Panel       |

| FP         | A14                        | I6/O5 |           | Frame Pulse for Flat Panel       |

|            |                            |       |           | Timing Control                   |

| LP         | A13                        | I6/O5 |           | Line Pulse for Flat Panel Tim-   |

|            |                            |       |           | ing Control                      |

| FPD[35:29] | E1, E2, E3, E4, D1, D2, C1 | I6/O5 |           | Flat Panel Data[35:29]           |

| FPD[28:25] | C2, B1, A1, D4             | I6/O5 | TEST[3:0] | Flat Panel Data[28:25] or        |

|            |                            |       |           | Test Selection pins 3-0          |

| FPD[24]    | A2                         |       |           | Flat Panel Data[24]              |

| FPD[23:0]  | C4, D5, A3, B4, A4, A5,    | 16/05 | VDO[23:0] | Flat Panel Data[23:0] or digital |

|            | A6, C6, D6, A7, B7, D7,    |       |           | data for TV/TMDS/LVDS            |

|            | A8, D8, A9, C9, D9, A10,   |       |           |                                  |

|            | B10, D10, A11, D11, A12,   |       |           |                                  |

|            | C12                        |       |           |                                  |

| FPDE       | D14                        | I6/O5 |           | Flat Panel Display Enable        |

| FPVCC      | B13                        | I6/O3 |           | Flat Panel VCC Control           |

| FPVEE      | D12                        | I6/O3 |           | Flat Panel VEE Control           |

| FPBL       | A15                        | 1605  |           | Flat Panel Back Light Control    |

\*See Pad Description, Section 3.1.12

Note: Switching pin function to Alternate Function is controlled by register, except for FPD[28:25], which are switched to test function by TEST# (pin C15).

# 3.1.3 ROM Interface

| Signal     |                |                  | POWER-UP      | Alternate |                                 |

|------------|----------------|------------------|---------------|-----------|---------------------------------|

| Name       | Pin #          | I/O <sup>3</sup> | Configuration | Function  | Description                     |

| ROMA [7:6] | E20, C22       | 17/04            |               | VDO[7:6]  | ROM Address [7:6] <sup>1</sup>  |

| ROMA [5:0] | B23, A23, A22, | I6/O3            |               | VDO[5:0]  | ROM Address [5:0] <sup>1</sup>  |

|            | D20, A21, B21  |                  |               |           |                                 |

| ROMA8      | C23            | 17/04            | CONFIG[0]     | VDO8      | ROM Address [8] <sup>1,2</sup>  |

| ROMA9      | D22            | 17/04            | CONFIG[1]     | VDO9      | ROM Address [9] <sup>1,2</sup>  |

| ROMA10     | E21            | 17/04            | CONFIG[2]     | VDO10     | ROM Address [10] <sup>1,2</sup> |

| ROMA11     | F20            | 17/04            | CONFIG[3]     | VDO11     | ROM Address [11] <sup>1,2</sup> |

| ROMA12     | D23            | 17/04            | 32K/64K ROM   | VDO12     | ROM Address [12] <sup>1,2</sup> |

| ROMA13     | E22            | 17/04            | INT/EXT PLL   | VDO13     | ROM Address [13] <sup>1,2</sup> |

| ROMA14     | F21            | 17/04            | INT/EXT       | VDO14     | ROM Address [14] <sup>1,2</sup> |

|            |                |                  | SCLK          |           |                                 |

| ROMA15     | E23            | 17/04            | AGP/PCI       | VDO15     | ROM Address [15] <sup>1,2</sup> |

| ROMD[7:4]  | C20, A20,      | I6/O3            |               |           | ROM Data [7:4] <sup>1</sup>     |

|            | D19, A19       |                  |               |           |                                 |

| ROMD3      | D18            | I6/O3            |               | HSYNC2    | ROM Data [3] <sup>1</sup>       |

| ROMD2      | A18            | I6/O3            |               | VSYNC2    | ROM Data [2] <sup>1</sup>       |

| ROMD1      | D17            | I6/O3            |               | DCLK2     | ROM Data [1] <sup>1</sup>       |

| ROMD0      | A17            | I6/O3            |               | BLANK2#   | ROM Data [0] <sup>1</sup>       |

| ROMFW#     | D15            | I6/O3            |               |           | Flash ROM Flash Write Command   |

| ROMOE#     | D16            | I6/O3            |               |           | ROM Output Enable               |

| ROMXW#     | A16            | I6/O3            |               |           | Peripheral I/O Write Command    |

| ROMXR#     | B16            | I6/O3            |               |           | Peripheral I/O Read Command     |

Note: 1. These pins have alternate functions as shown in the Alternate Pad Functions section below.

- 2. These pins have configuration functions at power-up. See the Alternate Pad Functions section below.

- 3 See Pad Description, Section 3.1.12

### 3.1.4 ZV Port

| Signal Name | Pin #                                     | I/O*  | Description                       |

|-------------|-------------------------------------------|-------|-----------------------------------|

| ZVPCLK      | L21                                       | 11    | ZV Port Pixel Clock               |

| ZVHREF      | T21                                       | 17/04 | ZV Port Horizontal Refresh (Sync) |

| ZVVSYNC     | T20                                       | 17/04 | ZV Port Vertical Sync             |

| ZVUV[7:0]   | N20, N21, N23, M20, M21,<br>M22, M23, L20 | 17/04 | ZV Port UV Data [7:0]             |

| ZVY[7:0]    | T23, R20, R21, R22, R23,<br>P20, P22, P23 | 17/04 | ZV Port Y Data [7:0]              |

| ZVCREF      | U23                                       | 17/04 | For Philips 7110/7111 Chips       |

\*See Pad Description, Section 3.1.12

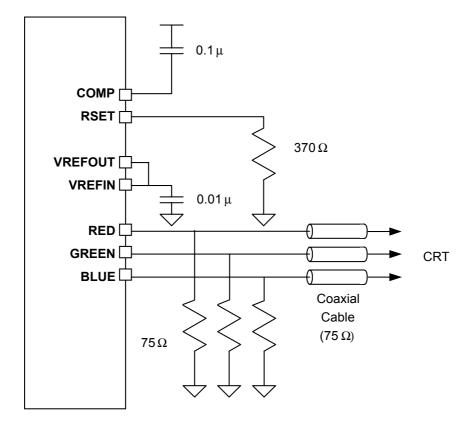

# 3.1.5 CRT Interface

| Signal Name | Pin # | I/O*  | Description                        |

|-------------|-------|-------|------------------------------------|

| RED         | V4    | AO    | Analog RED Output                  |

| GREEN       | V3    | AO    | Analog GREEN Output                |

| BLUE        | W1    | AO    | Analog BLUE Output                 |

| RSET        | U4    | Al    | DAC Full-scale Adjustment Resistor |

| COMP        | V1    | Al    | DAC Compensation Input             |

| DCLK        | T1    | I6/O3 | Pixel Clock                        |

| HSYNC       | U2    | O3    | Horizontal Sync                    |

| VSYNC       | U1    | O3    | Vertical Sync                      |

| BLANK#      | T4    | O3    | Blank                              |

\*See Pad Description, Section 3.1.12

# 3.1.6 Reference Clock Input

| Signal Name | Pin # | I/O* | Description              |

|-------------|-------|------|--------------------------|

| XCLKI       | W21   | 14   | Crystal/Oscillator Input |

| XCLKO       | W20   | 01   | Crystal Output           |

\*See Pad Description, Section 3.1.12

# 3.1.7 Programmable I/O Pins

| Signal Name | Pin # | I/O*  | Description                                                    |  |

|-------------|-------|-------|----------------------------------------------------------------|--|

| CIO7        | K23   | I6/O3 | User Programmable Input/Output [7]                             |  |

| CIO6        | K22   | I6/O3 | User Programmable Input/Output [6]                             |  |

| CIO5        | K21   | I6/O3 | User Programmable Input/Output [5]                             |  |

| CIO4        | K20   | I6/O3 | User Programmable Input/Output [4]                             |  |

| CIO3        | L23   | I6/O3 | User Programmable Input/Output [3]/I <sup>2</sup> C Data Line  |  |

| CIO2        | L22   | I6/O3 | User Programmable Input/Output [2]/I <sup>2</sup> C Clock Line |  |

| CIO1        | R3    | I6/O3 | User Programmable Input/Output [1]/DDC2B Data Line             |  |

| CIO0        | R4    | I6/O3 | User Programmable Input/Output [0]/DDC2B Clock Line            |  |

\*See Pad Description, Section 3.1.12

# 3.1.8 Testing Pins

| Signal Name | Pin #                                     | I/O* | Description                             |

|-------------|-------------------------------------------|------|-----------------------------------------|

| TEST#       | C15                                       | 11   | Test Mode. Not connected in normal use. |

| IOTST[8:1]  | H20, H22, H23, G20,<br>G21, G22, G23, F23 | O5   | Eight outputs for I/O testing.          |

\*See Pad Description, Section 3.1.12

Note: These pins are for testing use only.

### 3.1.9 Reserved Pins

| Signal Name    | Pin #                                                                                                                                                               | Description               |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Reserved[23:1] | R2, R1, J2, J4, H1, H2, H3, H4, G1, G2,<br>G4, F1, F3, F4, J23, J21, J20, AB21, Y17,<br>Y12, AA7, P4, P3, P1, N4, N2, N1, M4, M3,<br>M1, L1, L2, L4, K1, K3, K4, J1 | Reserved. Do not connect. |

# 3.1.10 Digital Power and Ground Pins

| Signal<br>Name | Pin #                                                                                                                                                                                                                                                | Description                                         |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| VDD_IO         | B2, B5, B8, B11, B15, B18, B22, F2, F22, J22,<br>K2, P2, AA2, AA22, AB5, AB9, AB13, AB17                                                                                                                                                             | 18 of 3.3V power pins for I/O pads                  |

| VDD_C          | M2, N22, T2, T22, AB3, AB7, AB11, AB15, AB20                                                                                                                                                                                                         | 9 of 2.5V power pins for core circuit               |

| GND            | C3, C7, C10, C14, C17, D3, D21, G3, H21, J3,<br>K10, K11, K12, K13, K14, L3, L10, L11, L12, L13,<br>L14, M10, M11, M12, M13, M14, N3, N10, N11,<br>N12, N13, N14, P10, P11, P12, P13, P14, P21,<br>T3, U22, AA10, AA14, AA18, AA21, AA3, AA6,<br>AB1 | 47 Digital ground pins                              |

| VDD_R          | B3, B6, B9, B12, B14, B17, B19, B20                                                                                                                                                                                                                  | 8 of 2.5V power pins for internal<br>memory modules |

| GND_R          | C5, C8, C11, C13, C16, C18, C19, C21                                                                                                                                                                                                                 | 8 ground pins for internal memory modules           |

| VDD_P          | U20                                                                                                                                                                                                                                                  | Digital 2.5V for PLL of MCLK,<br>DCLK, and PCLK     |

| GND_P          | U21                                                                                                                                                                                                                                                  | Digital ground for PLL of MCLK,<br>DCLK, and PCLK   |

| VDD_S          | Y2                                                                                                                                                                                                                                                   | Digital 2.5V for system clock DLL                   |

| GND_S          | Y3                                                                                                                                                                                                                                                   | Digital ground for system clock PLL                 |

# 3.1.11 Analog Power and Ground Pins

| Signal Name | Pin #         | Description                        |  |

|-------------|---------------|------------------------------------|--|

| AVDD_P      | W22, V22, V21 | 3 analog power pins for PLL        |  |

| AGND_P      | W23, V23, V20 | 3 analog ground pins for PLL       |  |

| AVDD_D      | U3, W2        | 2 analog power pins for DAC        |  |

| AGND_D      | V2, W3        | 2 analog ground pins for DAC       |  |

| AVDD_S      | W4            | Analog power for system clock DLL  |  |

| AGND_S      | Y1            | Analog ground for system clock PLL |  |

# 3.1.12 Pad Descriptions

| I/O   | I/O  | Internal | Tri-State | Current | Capacitance | Note                           |

|-------|------|----------|-----------|---------|-------------|--------------------------------|

| Туре  |      | Pull Up  |           | (mA)    | (pF)        |                                |

| 11    | 1    |          |           |         | 7.337       | Clock Pad                      |

| 12    | I    |          |           |         | 7.346       |                                |

| 13    | I    |          |           |         | 7.346       | Schimitt-triggered             |

| I4/O1 | I/O  | N        | N         |         |             | OSC Pad                        |

| I5/O2 | I/O  | N        | N         | 24      |             |                                |

| I6/O3 | I/O  | N        | Y         | 4       | 7.754       |                                |

| 17/04 | I/O  | Y        | Y         | 4       | 7.755       |                                |

| 17/04 | I/O  | Y        | Y         | 4       | 7.754       |                                |

| I6/O5 | I/O  | N        | Y         | 8       | 7.387       | Limited Slew Rate              |

| I6/O3 | I/O  | N        | Y         | 4       | 7.754       |                                |

| I6/O5 | I/O  | N        | Y         | 8       | 7.387       |                                |

| O6    | 0    | N        | Y         | 2       | 7.755       |                                |

| O3    | 0    | N        | Y         | 4       | 7.754       |                                |

| AI    | Ana  |          |           |         |             | Analog Signal Pad, Input       |

| AO    | Ana  |          |           |         |             | Analog Signal Pad, Out-<br>put |

|       | Pwr  |          |           |         |             | Digital Power, 2.5V            |

|       | Pwr  |          |           |         |             | Digital Power, 3.3V            |

|       | APwr |          |           |         |             | Analog Power                   |

|       | Gnd  |          |           |         |             | Digital Ground, 2.5V           |

|       | Gnd  |          |           |         |             | Digital Ground, 3.3V           |

|       | AGnd |          |           |         |             | Analog Ground                  |

### 3.1.13 Alternate Pad Function

| Signal     |                                                                                                                   |                  | Alternate       |                                                            |

|------------|-------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------------------------------------------------|

| Name       | Pin #                                                                                                             | I/O <sup>3</sup> | Function        | Description                                                |

| ROMA [7:6] | E20, C22                                                                                                          | 17/04            | VDO[7:6]        | Digital Data[7:6] for TV/TMDS/LVDS<br>Encoder <sup>1</sup> |

| ROMA [5:0] | B23, A23, A22, D20,<br>A21, B21                                                                                   | I6/O3            | VDO[5:0]        | Digital Data[5:0] for TV/TMDS/LVDS<br>Encoder <sup>1</sup> |

| ROMA8      | C23                                                                                                               | 17/04            | VDO8            | Digital Data[8] for TV/TMDS/LVDS Encoder <sup>1</sup>      |

| ROMA9      | D22                                                                                                               | 17/04            | VDO9            | Digital Data[9] for TV/TMDS/LVDS Encoder <sup>1</sup>      |

| ROMA10     | E21                                                                                                               | 17/04            | VDO10           | Digital Data[10] for TV/TMDS/LVDS Encoder <sup>1</sup>     |

| ROMA11     | F20                                                                                                               | 17/04            | VDO11           | Digital Data[11] for TV/TMDS/LVDS Encoder <sup>1</sup>     |

| ROMA12     | D23                                                                                                               | 17/04            | VDO12           | Digital Data[12] for TV/TMDS/LVDS Encoder <sup>1</sup>     |

| ROMA13     | E22                                                                                                               | 17/04            | VDO13           | Digital Data[13] for TV/TMDS/LVDS Encoder <sup>1</sup>     |

| ROMA14     | F21                                                                                                               | 17/04            | VDO14           | Digital Data[14] for TV/TMDS/LVDS Encoder <sup>1</sup>     |

| ROMA15     | E23                                                                                                               | 17/04            | VDO15           | Digital Data[15] for TV/TMDS/LVDS Encoder <sup>1</sup>     |

| ROMD3      | D18                                                                                                               | I6/O3            | HSYNC2          | HSYNC for TV/TMDS/LVDS Encoder <sup>1</sup>                |

| ROMD2      | A18                                                                                                               | I6/O3            | VSYNC2          | VSYNC for TV/TMDS/LVDS Encoder <sup>1</sup>                |

| ROMD1      | D17                                                                                                               | I6/O3            | DCLK2           | DCLK for TV/TMDS/LVDS Encoder <sup>1</sup>                 |

| ROMD0      | A17                                                                                                               | I6/O3            | BLANK2#         | BLANK# for TV/TMDS/LVDS Encoder <sup>1</sup>               |

| FPD[28:25] | C2, B1, A1, D4                                                                                                    | I6/O5            | TEST[3:0]       | Test Selection pins 3-0                                    |

| FPD[23:0]  | C4, D5, A3, B4, A4,<br>A5, A6, C6, D6, A7, B7,<br>D7, A8, D8, A9, C9, D9,<br>A10, B10, D10, A11,<br>D11, A12, C12 | 16/05            | VDO[23:0]       | Digital data for TV/TMDS/LVDS Encoder <sup>1</sup>         |

| ROMA8      | C23                                                                                                               |                  |                 | Power-up configuration pin <sup>2</sup>                    |

| ROMA9      | D22                                                                                                               |                  |                 | Power-up configuration pin <sup>2</sup>                    |

| ROMA10     | E21                                                                                                               |                  |                 | Power-up configuration pin <sup>2</sup>                    |

| ROMA11     | F20                                                                                                               | 17/04            | CONFIG[3]       | Power-up configuration pin <sup>2</sup>                    |

| ROMA12     | D23                                                                                                               | 17/04            | 32K/64K<br>ROM  | Power-up configuration pin <sup>2</sup>                    |

| ROMA13     | E22                                                                                                               | 17/04            | INT/EXT<br>PLL  | Power-up configuration pin <sup>2</sup>                    |

| ROMA14     | F21                                                                                                               | 17/04            | INT/EXT<br>SCLK | Power-up configuration pin <sup>2</sup>                    |

| ROMA15     | E23                                                                                                               | 17/04            | AGP/PCI         | Power-up configuration pin <sup>2</sup>                    |

Note:

- 1. TMDS : Transition Minimized Differential Signaling LVDS : Low Voltage Differential Signaling

- 2. Used for power-on configuration strapping <u>and</u> in TV encoding. For information about enabling the alternate function see the Application Note for each function.

- 3. See Pad Description, Section 3.1.12

| 3.1.14<br>Pin Assignment<br>(by pin number) |             |  |

|---------------------------------------------|-------------|--|

|                                             | Signal Name |  |

| A1                                          | FPD26       |  |

| A2                                          | FPD24       |  |